Progress:

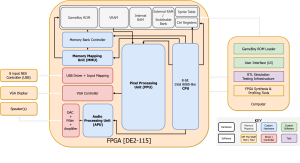

- CPU:

- Multicycle CPU framework completed

- Instructions implemented: 11

- Instruction tests written: 23

- PPU

- RTL updated based on Memory organization / controller related design updates.

- Implemented testbench, Python script to render image based on frame dump.

- Unit tested most of the design and parts of the integrated logic. Working on debugging the PPU with a full end-to-end test.

- MMU

- Re-designed memory controller to utilize FPGA Block RAMs instead of DE II SRAM/SDRAMs for simplicity of integration

- Synthesized and tested Block Rams of different sizes (in ROM and RAM variant) and confirmed that they work

- Creating Memory Controller according to updated spec (DMA support)

- Other I/O

- Did research into USB/Audio integration. Discovered that NIOS II cannot be used, but there are IPs provided by Altera that use an Avalon master/slave interface.

- Learned more about the Quartus Avalon Slave Interface, currently working to create unit tests

- Swapped to cycle-accurate multicycle CPU.

- Reworked DMA responsibility

Risks and Risk Management:

- Many CPU instructions are listed as TODO in “Gameboy: Complete Technical Reference”

- Will look at Intel 8080 and software emulators to fill in the blanks.

Part A – Katherine (public health, safety or welfare):

Our Gameboy will be made as a larger system, similar to a desktop computer, with a larger screen and controller. This will help reduce eye strain, making it easier for users to play games, especially for those with visual impairments. The larger controller will also improve accessibility for people with limited mobility. These modifications will make gameplay less physically taxing, hence improving overall safety.

Part B – Ruslana (social factors):

Our capstone responds to social factors because we intend to make playing the Gameboy an all-inclusive experience at demo day, where anybody can go and engage with the video games. Furthermore, we are preserving the Gameboy’s heritage and legacy by showing others the original and first console ever made that has paved the way for modern ubiquitous consoles all around us today (such as the Switch, Playstation, Xbox, etc.). People who have experienced the original Gameboy and curious younger generations can be both entertained and learn about our hardware implementation for this project.

Part C – Bharathi (economic factors):

Our project offers a cost-effective and sustainable way to preserve and play retro games without relying on original hardware which can be difficult to find, maintain, or upgrade. Unlike a single-purpose handheld console, our FPGA-based design can be upgraded and modified over time without additional hardware costs. Our project also encourages the digital distribution and consumption of retro games through legally obtained ROMs, reducing need for physical cartridges that may become may be hard to find / use.