Progress:

- Integration

- Full integration in progress

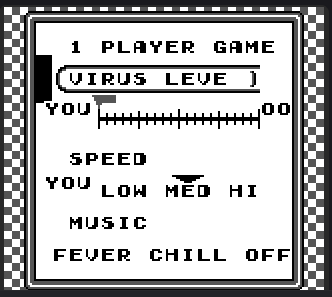

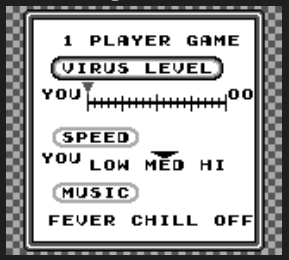

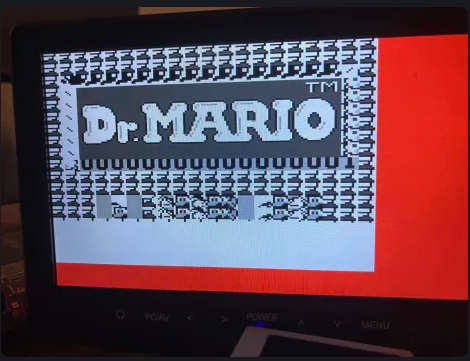

- We are able to render specific frames statically with Tetris/Dr.Mario/other rom tests in simulation now, but rendering the full game code in synthesis is still being debugged.

- Successfully generated first frame for Tetris in simulation.

- Successfully generated 3 frames for Dr Mario using actual Joypad interrupts in simulation.

- VGA Support added in synthesis.

- Full design (including controller) integrated and synthesized on FPGA — debugging (using SignalTap 🙁 ) in progress.

- DMG Acid Test face runs and shows up as a mostly intact fact on synthesized design

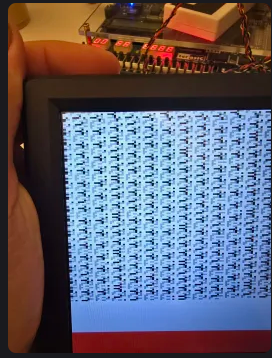

- Dr. Mario ROM in synthesis has yet to work–after starting it up on an FPGA, the first frame shows up as a flicker and then it’s a white screen. We are fixing this currently.

- We are able to render specific frames statically with Tetris/Dr.Mario/other rom tests in simulation now, but rendering the full game code in synthesis is still being debugged.

- Full integration in progress

- PPU: DMG Acid Test in simulation almost fully debugged. PPU integrated with design fully. VGA + BRAM based Frame Buffer support added.

- APU:

- Wrote/compiled APU (4 channels, 2 PWM, 1 wave ram, 1 pseudorandom with envelope/sweep/frequency change support)

- I/O

- New controllers have been assembled

Design Changes:

- There are now 4 clocks in the design.

- MMU clock that runs at 8MHz

- PPU clock that runs at 4MHz (1 cycle is called a dot)

- CPU clock that runs at 1MHz (1 M-cycle = 4 dots)

- VGA clock that runs at 50MHz

- The reason for these clocks is due to the spec.

- The MMU must run twice the CPU frequency, because our FPGA BRAMS (gameboy memory) have a 2 cycle read latency.

- The PPU is clocked at 4 MHz according to Gameboy spec

- The CPU executes an instruction across 4 cycles of the 4 MHz clock–hence, we made the CPU clocked according to 1 MHz. This is a subtle distinction that took us a while to dig out during integration and clarify. The discrepancy between the CPU and PPU clocks are documented poorly online and likely isn’t as big of a concern for software emulators.

- The VGA must communicate at 50 MHz.

- The MMU must run twice the CPU frequency, because our FPGA BRAMS (gameboy memory) have a 2 cycle read latency.

- In our FPGA, we have two clock generators – a 50 MHz one and an 8 MHz one. The other 4 MHz and 1 MHz signals are derived from the 8 MHz to ensure that the clock edges are properly aligned. This was another bug we fixed this week.

Risks and Risk Management:

- Switching to Joypad GPIO for now to reduce USB integration complexity

- Postponing NIOS II integration for after MVP gets hit, especially because its more well understood now

- Potentially cutting APU from final, because of time considerations (even though the pieces to put it together exist)

Verification & Validation Progress:

- CPU:

-

-

- passes Blargg Test ROM cpu-tests (minus interrupt tests due to optimizations in PPU)

- passes hand-made tests

- Is able to generate multiple frames and process joypad input.

-

- PPU:

-

-

- Passes mode-level, line-level, and frame level timing requirements

- 100% palette mapping accuracy

- Minor Sprite bugs – but these will be debugged soon to achieve sprite accuracy requirement

- Frame Output latency well under requirement threshold

-

- MMU:

-

-

- Passes in personal testbench that did:

- Queries to memory regions (rom/wram/exram/vram/oam/hram)

- Queries to memory IO registers

- DMA Query

- Basic interrupt checks

- Passes in personal testbench that did:

-

- APU: Work in progress – no tests have been done so far

- I/O:

- All key presses on the controller are very responsive – complete testing of latency will be done soon to validate if controller response time meets use case and design requirements.

Bugs we fixed over the last two weeks:

- VRAM/OAM cpu write propagation (simulation)

- Reworked MMU/CPU/PPU clocks (simulation/synthesis)

- PPU reset behavior (simulation)

- Sprite priority bugs (simulation)

- Sprite horizontal and vertical flipping bugs (simulation)

- Window internal counter bug (still needs to be fully fixed) (simulation)

- Sprite sorting edge case (when sprite is technically off screen) (simulation)

- Horizontal and vertical background scrolling glitch (simulation)

- Fixed clock misalignment issue between PLLs on FPGA (synthesis)

- HRAM access issue (simulation)

- VGA upscaling issue (synthesis)

- VGA frequency issue, had to reparameterize to fit different resolution specs (synthesis)

- Joypad reading bug (simulation)

- Joypad register writing bug (simulation)

- Color Palette map bug (simulation)

- Lingering `DOC flag that took 4 hours to find (synthesis)

- I hate signaltap

- LCDC reset condition bug (simulation)

- Improper LY increment bug (simulation)

- Timer bug (simulation)

- IE IF register bug (simulation)

- STOP instruction bug (simulation)

- STAT interrupt and LY==LYC flag bug (simulation)

- TMA and TIMA mapping bug (simulation)

Known bugs that need be fixed:

- Simulation: DMG Acid Test – tile flipping bug

- Simulation: DMG Acid Test – window internal line counter bug (off by 1 line)

- Simulation: Dr. Mario – Frame 3 – Mario’s right hand is missing (overlapping sprite case)

- Synthesis: Dr. Mario’s first frame from ROM has yet to show up successfully. It flickers on FPGA screen and vanishes currently.