Accomplished:

- Verified MMU and CPU are integrated with all except interrupt tests (which we are now working on, due to also adding the PPU)

- Integrated all units but APU

- Made a testbench to test full integration

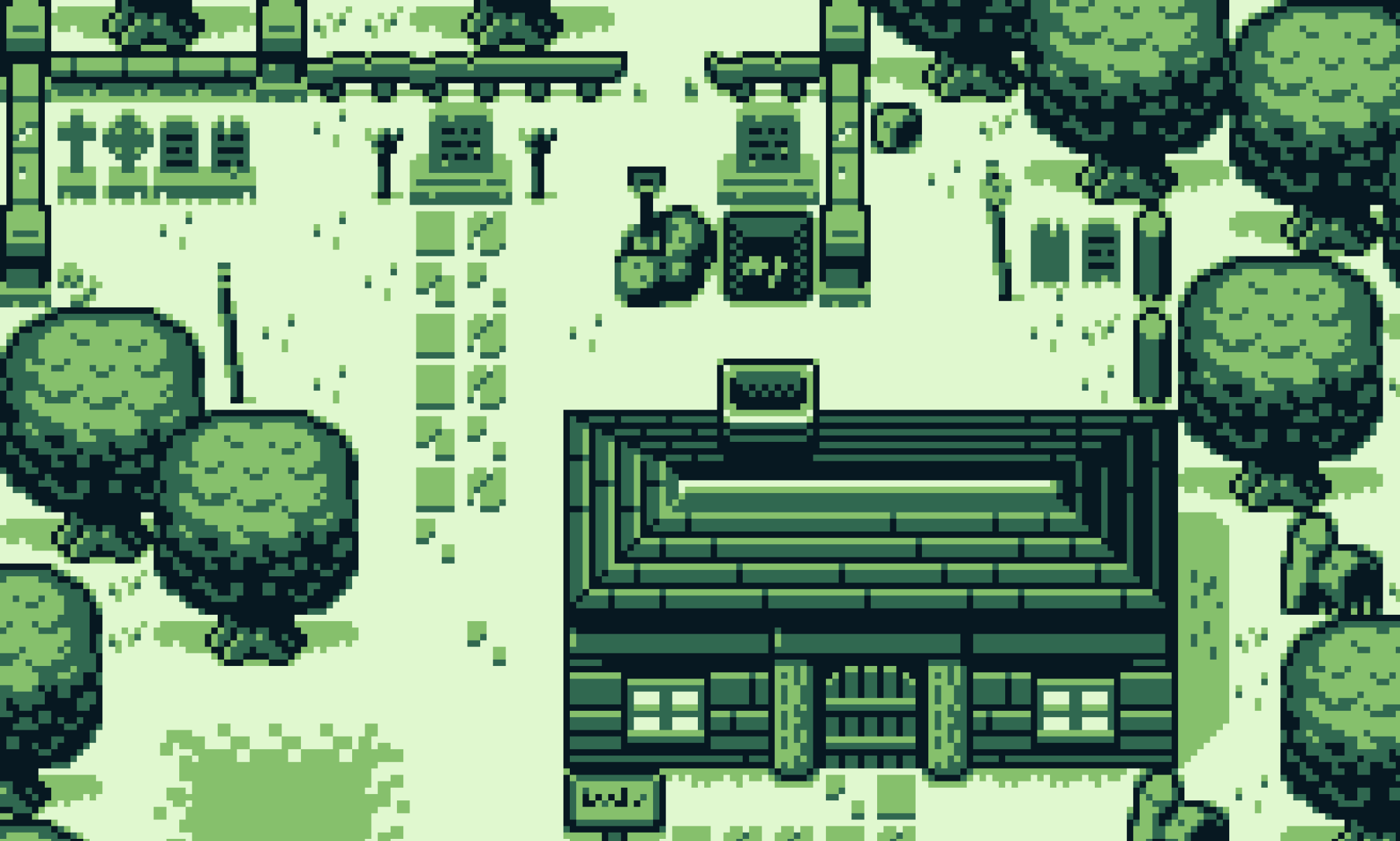

- Started debugging all units with Tetris and dmg-acid-test

- Synthesized all units on Quartus. After catching some latches, we confirmed that it is indeed synthesizable. We are using the amount of memory that we expect, but surprisingly, there is low LUT usage. Hopefully, this is not an indication that stuff is being optimized away, but the Technology RTL Viewer on Quartus is showing all of the circuitry and fllip-flops for our 3 designs.

Next Step:

- Work on debugging Tetris

Other Notes or Concerns:

- We are on schedule.

- The blargg interrupt tests can’t be fully run due to timing optimizations done to the PPU. However, what was able to be run shows that interrupts will probably work.

- Most MMU bugs have been subtle address calculation problems or actual differing interpretations of spec details that are getting noticed with each test, but no enormous internal failures. It is servicing the PPU and CPU fine.