Progress:

- Tetris is playable, with fully working controller inputs, but runs at ~4* speed

- Found a timer initialization and incrementation bug.

Risks and Risk Management:

- FPGA debugging is a very “guess and hope for the best” process, even with signal-tap.

Tests:

- CPU

- Handmade test for every Gameboy instruction

- Blarrg cpu-instrs tests run on CPU.

- Fixed some misunderstandings of Gameboy specification details.

- PPU

- Basic static frames from Tetris/Dr. Mario with fixed tile/sprite preloaded memory

- Dmg-Acid tests on Simulation

- Basic static frames from MMU/CPU/PPU integration

- MMU

- Basic testbench checks on synchronous cycle BRAM accesses (R/W)

- Synchronous cycle I/O registers (PPU/APU/Interrupt) (R/W)

- Basic timer register checks

- Simulation

- Blarg cpu-instrs tests.

- Many MMU bugs fixed

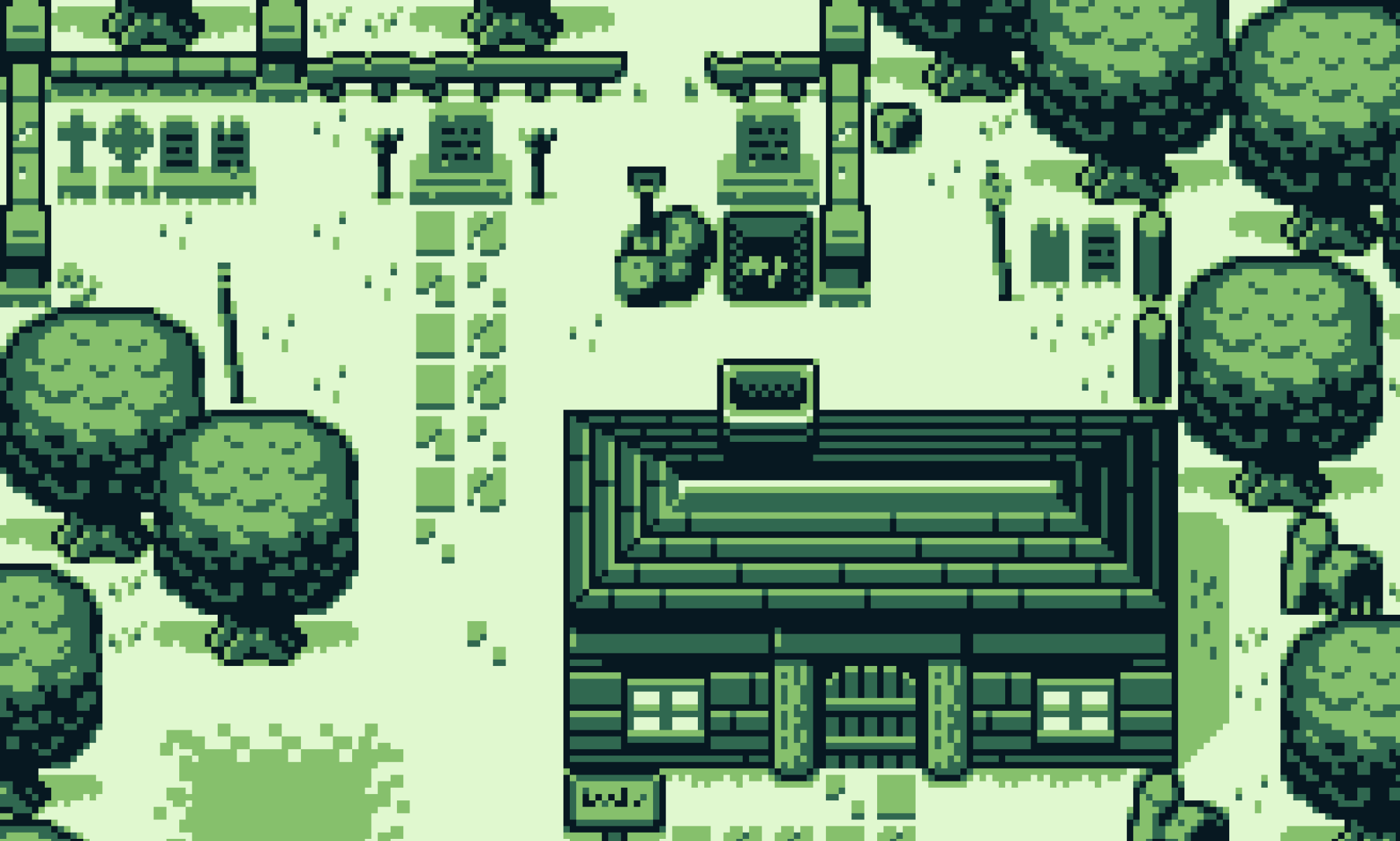

- 1st pre-loaded frame of Tetris test.

- 1st Tetris frame generation test.

- 3 clocks were added to the design

- CPU IME (interrupt enable) register misunderstanding fixed.

- Many MMU bugs fixed

- 1st, 2nd, 3rd frame + controller input test on Dr. Mario.

- Fixed PPU palette issue

- Joycon register spec misunderstanding fixed.

- Many MMU bugs fixed

- Blarg cpu-instrs tests.

- Physical

- Basic controller button to LED test

- DMG-Acid test rendering

- Fixed jagged clock issues (ensured that clocks were derived off of others for adequate timing)

- “Play” Dr. Mario.

- Synthesis results in non-deterministic behavior.

- Play Tetris

- Joycon issue determined via patterns and fixed.