Progress:

- Integration

- MMU and CPU have been integrated

- Testbench made for MMU and CPU integration

- MMU and CPU integration debugging is in process.

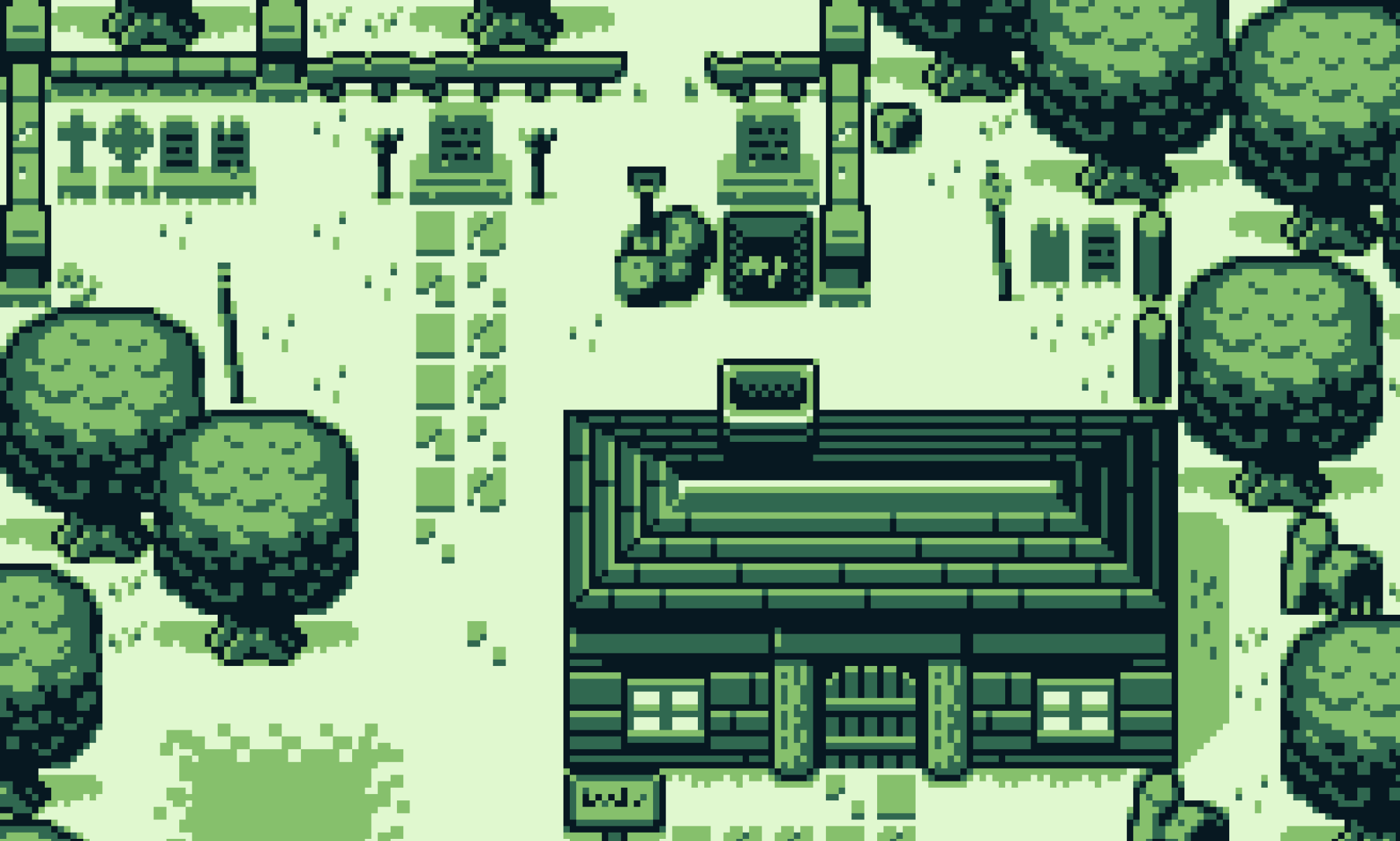

- PPU

- CGB PPU debugging — backgrounds and windows works.

- MMU

- BRAM works in testbench

- IO timer/apu/ppu/interrupt registers work in testbench

- debugging DMA transfer details but CPU/MMU integration has begun

- APU

- Implemented I2S logic — works in simulation.

- Sketched APU datapath + RTL.

- I/O

- New controller has been assembled

Design Changes:

- Continuing along with clock at 2x CPU frequency for MMU, given that MMU BRAMs have to read out in 2 clock cycles (and we are expecting single cycle delay in CPU case)