Accomplished

My goal for this week (and break) was to mainly finish debug the PPU and get started on the full color implementation.

DMG PPU (4-color PPU)

- I spent most of my time this week on getting the DMG PPU fully functional—and I was pretty successful! I decided to rewrite the testbench so that it would also generate the final image (in PPM format) so I wouldn’t need to use a Python script. This sped-up my debugging progress considerably.

- The other main breakthrough with debugging came in the form of SameBoy (GameBoy emulator), which I used to get the VRAM data and the OAM data for each frame. This method is not perfect as it doesn’t really give me information for crucial control registers that can change on a line by line basis. However, it helped me find many of the weirder bugs in my PPU a lot more quickly.

SameBoy Emulator - The DMG PPU is very close to being done. I still have minor issues with certain sprite and scrolling edge cases, however these frames (or sequence of frames) involve CPU writes to VRAM so I have no way of verifying if the issue is with my RTL or simply because I don’t have the perfect snapshot of the memory.

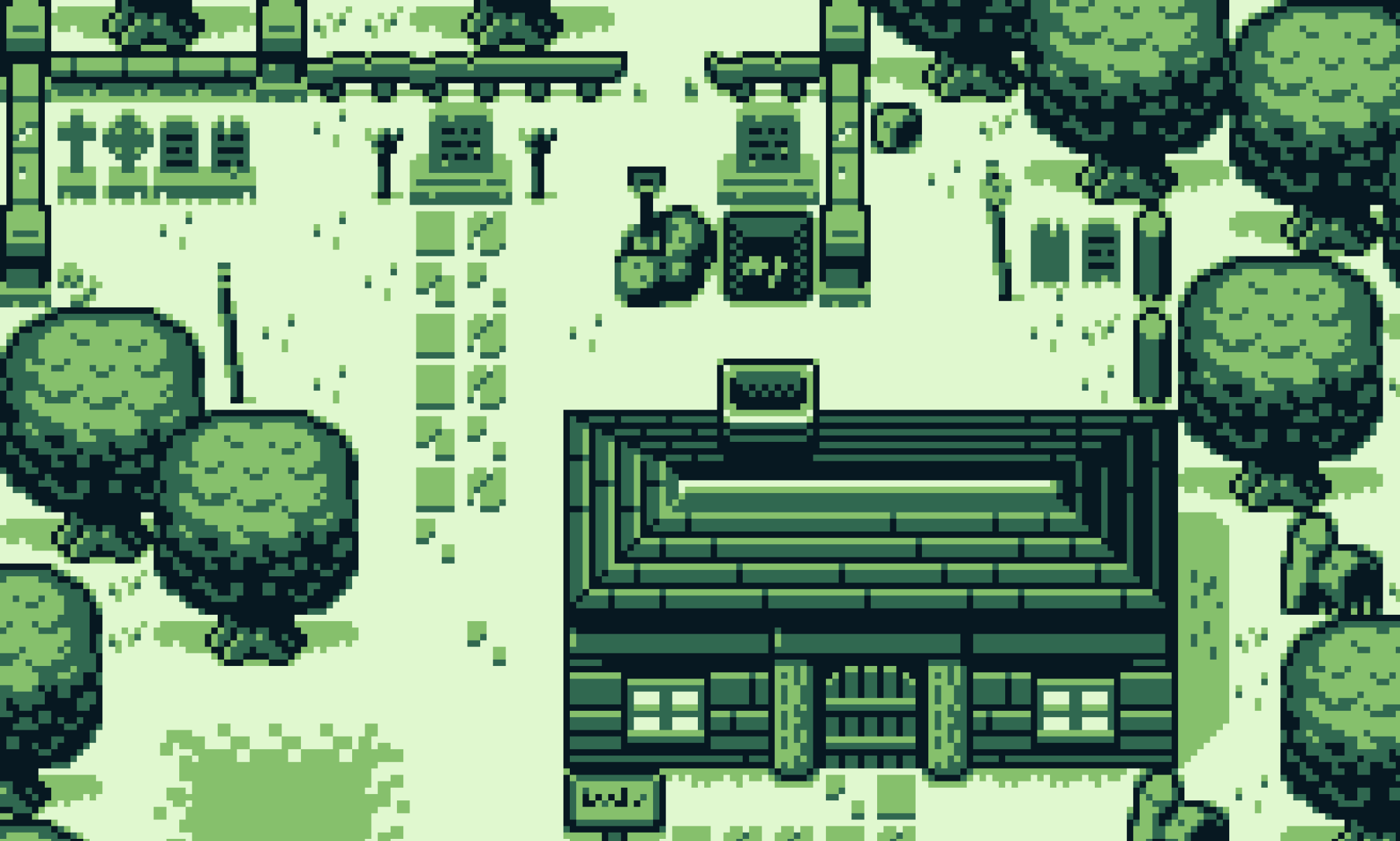

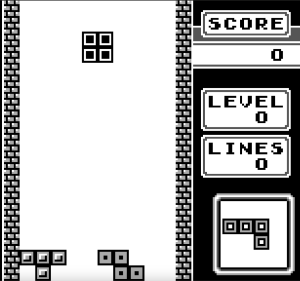

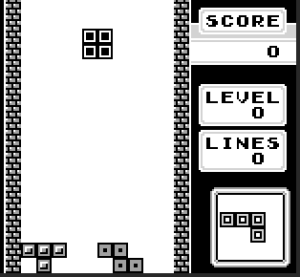

- In summary, I’m pretty happy with the progress and feel confident moving onto working on the full-color PPU. Here are some frames I rendered this week:

Tetris — Reference (from SameBoy)

Tetris — Frame I rendered

CGB PPU (full-color PPU)

I used the information I collected during the prior week to make the necessary updates for the full-color PPU. Because of my modular design of the rendering pipeline, I am able to make changes on the DMG PPU but still treat the layers as “black boxes” in some sense and extrapolate to make the CGB PPU integrated with larger memory sizes, many more color palettes and many new edge cases.

APU / CODEC Research

Given the NIOS / Quartus based roadblock we hit last week, I spent some time researching alternative solutions with Ruslana. The most promising approach is directly using the CODEC (WM8731) without using the NIOS softcore by configuring the registers on the WM8731 using i2c and then transferring the actual data using i2s. This appeared to be quite complex at first, especially because we weren’t able to find any evidence that someone else had managed to do this. But we’ve recently found some labs (form digital design classes at other universities who also using the same FPGA) that implement different fragments of the logic on the WM8731 directly.

I plan to use very simple i2c based test with the WM8731 to see if we get an ACK after a write to the reset register on WM8731. This should help us evaluate on the feasibility of using this approach for the APU.

Design Report

I also spent a decent chunk of time working on the design report the week it was due. We ended up working almost until the deadline as we received some crucial feedback from our design presentation somewhat late, but we were able to make the necessary updates before the deadline.

Summary of time spent (Week of 2/23 to 3/1):

- Researching how to use WM8731 (Audio CODEC on the DE2-115): 6 hrs

- Design Review Report: 8 hrs

Summary of time spent (Week of 3/2 to 3/8):

- Writing new testbench: 2 hrs

- PPU debugging + VGA testing : 12 hrs

- Full-color (CGB) implementation: 3 hrs

- Writing I2C based sound check test for the WM8731: 2 hrs

Schedule / Progress

Overall I’m on schedule or maybe slightly ahead as I feel relatively confident about the correctness of the DMG PPU (wrt to our MVP games — Tetris and Dr Mario should both be pretty much correct as they have no scrolling). I will also likely be spending some sizable amount of time on the APU from this week onwards as that remains as our largest unknown at the moment.

Next Step(s)

My goal(s) for next week are some subset of:

- Get DMG PPU integrated with CPU (if CPU gets integrated with memory)

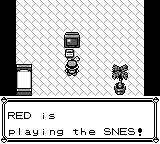

- Fix scrolling / sprite bug in Pokemon Red:

- Debug CGB PPU

- Attempt to read from and write to WM8731 using i2c and get some confirmation that it was configured correctly.