This week I worked on making the final presentation slides with Amelia. I also worked on integrating the PCB as part of the whole system with the Verilog team. I also fixed some of the soldering work on a LED that wasn’t working too well – the “i” on the lampboard – by desoldering it and moving to another pin on the shift register.. Finally, I continued working on the final report.

Category: Status Reports

Nancy’s Status Report for 4/26

In the beginning of this week, I prepared for the final presentation and presented on Monday. Throughout the week, Amelia and I met to work on finalizing our integration between the RTL and the PCB. We were running into issues with our rotor settings (using the buttons and rotary encoder on the PCB). This took a lot of trial and error since it was hard to pinpoint what exactly was going wrong (the PCB itself, the individual modules, or their integration). We had made sure to test everything individually beforehand, so finally we realized the issue was the buttons on the PCB, since our implementation worked fine when we used the buttons on the DE-10 instead. We realized this was because we did not have any pull up or pull down resistors on the PCB. However, Amelia was able to work around this by having the buttons depressed while rotating the rotary encoder.

This upcoming week, we will finalize our poster, video, and report. I will also make sure we can demonstrate the RTL working on its own on the other DE-10 for demo purposes.

Team Status Report for 4/19

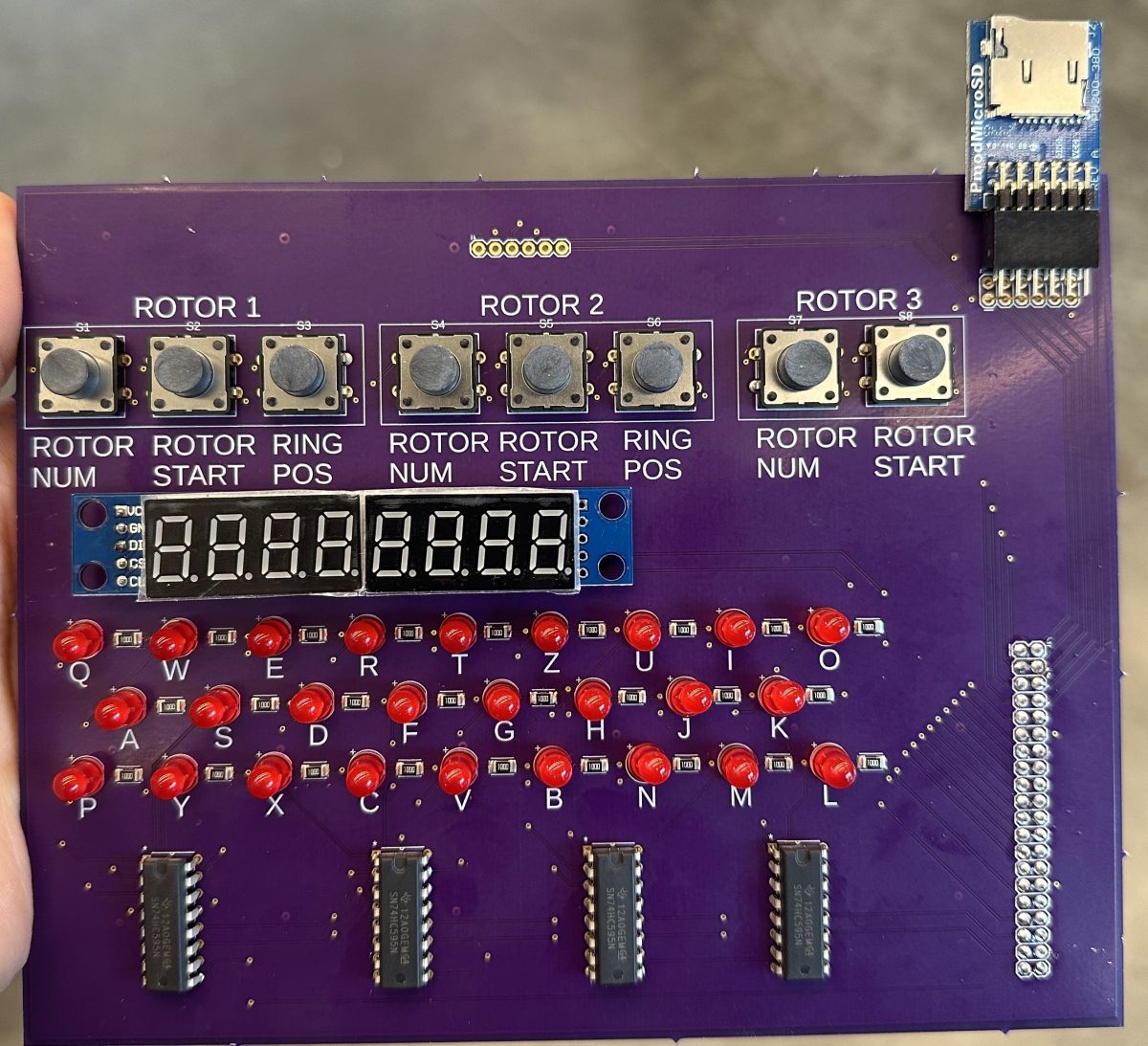

This week, we have made good progress towards integrating the PCB with the FPGA. Tanisha finished soldering the PCB and fixed one LED that was not lighting up by bypassing the trace and manually connecting an external wire/resistor to another output of the last shift register, which had unused outputs. She has verified the rest of the traces for continuity, setting us up for success when combining with the FPGA. One small issue is with the orientation of the rotary encoder, which we will need to finalize for aesthetic/functional purposes.

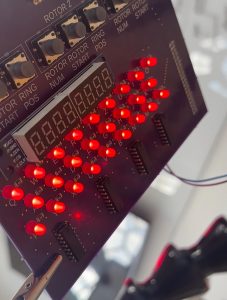

On the RTL side, Amelia and Nancy still have to work through some bugs with how the rotor settings are displayed on the external 7 segment display rather than on the DE10’s. We also hooked up the pins involving the display and the rotary encoder to the PCB and it was working the same! This was a good sign since we were concerned about if the FPGA’s 3V3 pin would be sufficient to power the PCB, but since the 7 segment display worked while all LEDs were illuminated, we should be good. We also got the lampboard to light up corresponding to our input from the PS/2, but still have some work to do with getting the output to display instead.

Finally, Amelia also worked on the housing for our FPGA & PCB. This was our solution to the loose header pins on the FPGA preventing us from getting a reliable connection. Since we are now using jumper wires between the two headers, we needed the PCB to be elevated above the FPGA, which also added some needed stability! Today, Amelia successfully laser cut the pieces and we will glue them together this week.

Tanisha’s Status Report for 4/19

This week I finished soldering our PCB and conducted PCB testing. I also started working on integration with the Verilog team.

I conducted extensive PCB testing throughout the week. I checked continuity for every connection on the board, checked each pin was supplying the appropriate power level, and power level at every connection and ensured it matches the schematic.

I also powered the PCB to ensure things were functioning and found all but one LED was working. I fixed this by trying to resolder the PCB, however in doing so I accidentally ruined a pad of the LED. However, I didn’t realise this at first so I worked on figuring out if the issue was with a dead LED, dead shift register, or a power issue.

By checking continuity and power outrages throughout the traces along the path of the power -> LED -> resistor -> ground, I was able to isolate the issue to be a lack of connection around the LED, hence realizing the pads were ruined. I solved this by incrementally soldering bare wire between the connections I wanted (power -> LED and LED -> resistor) till all connections were verified by both tests and finally the LED started working! The benefit of all of this means I am confident in the rest of my connections due to all of the debugging I did.

This is an example of skills I have learned over this past semester – trial and error by practicing my soldering and circuitry skills. I also learned more skills by asking other capstone groups for advice if they had encountered similar situations, I would say that was one of the most beneficial learning experiences I had. I also had practice outside of Capstone with TAing 18-349 where I had plenty of practice on laying out / fabricating and soldering PCBs.

The only task I have left for the PCB is fixing the rotary encoder as I laid the order of the pins out backwards on the schematic accidentally. I looked into a perf board solution to remedy this, but ultimately decided on adding another right angled header to try and change the direction of the encoder. I will also work on our final presentation and documentation for our final few submissions.

Amelia’s Status Report for 4/19

This was a very productive week! On Monday, Nancy and I fixed the bug we were facing last week with the rotary encoder not wrapping around from Z to A. We also added the RTL for the enigma rotor starting, rotor number, and ring position to display on the MAX seven segment display. We then implemented the rotary encoder modules with the rest of our integrated RTL. We are currently facing a few issues/glitches with the integration between how values are displayed on the MAX seven segment when the rotary encoder is turned.

On Wednesday, Tanisha had finished running tests on the completed PCB and Nancy and I worked on integrating the current code and started working on the lampboard shift register logic. On Friday, Nancy and I started working on the shift register logic — we started with a single shift register with 8 LEDs hooked up on a breadboard. By Friday afternoon, we finished expanding this to the full PCB lampboard, here is a video of the lamboard integrated with the FPGA + PS2 keyboard.

Also, on Wednesday, I also created a CAD model of the wood housing for the PCB and FPGA and laser cut it on Saturday. Below is a picture of the wood housing with the FPGA inside and the PCB mounted on top!

I have learned so much over the course of this semester. One of the first challenges was hooking up the FPGA with all of the peripherals which required learning how to decipher several protocols (PS2, SPI). To do this I looked through old git repos and read lots of documentation and datasheets. The RTL we wrote for this project was much different than in any of the other hardware classes I’ve taken so far because of all the integration we had to do. This RTL also had to be synthesized on real hardware (which I haven’t done since 240) which had its own share of issues and required lots of heavy debugging and time spent on Reddit forums. I also learned how to CAD and use the laser cut software (CoralDraw) this semester for laser cutting the housing. I watched videos online to figure out how to CAD using onShape. I also asked some of my mechanical engineering friends for tips on how to make box joints. For laser cutting in TechSpark, I asked TechSpark employees for help and other students for help using the machine.

Nancy’s Status Report for 4/19

This week, Amelia & I worked on integrating our RTL with our many I/O components. On Monday, we fixed our issue with the rotary encoder skipping over values when going A-Z on our 7 segment display and then moved on to getting the rotary encoder to control the actual rotor settings, not just proxy 1-8 and A-Z variables. This led to some strange glitches that we then worked on debugging, which we still need to finish. On Wednesday, we worked on connecting the DE10’s GPIO pins to the PCB itself. This led to some strange issues, like some of the GPIO pins on the FPGA itself not working as expected, even when we just tested it with breadboard components. However, since Tanisha had gotten the PCB components soldered, we wanted to start working on the shift registers for the lampboard to make sure that worked as well. So, on Friday Amelia & I worked on getting the lampboard to work. We first started with a single shift register on a breadboard, and after some debugging, we got the lampboard to successfully display letters we input from the PS/2! This week, we will finalize our presentation and work on fully integrating, including working through the bugs with the 7 segment display and getting the lampboard to display the encoded data, not the PS/2 input data.

Over the course of this semester, I have learned a lot from this project. When selecting the right components, FPGA, and overall implementation, I had to read a lot of datasheets and documentation. While we’ve been introduced to this in classes before, it was definitely more daunting since there was less guidance, but overall it has made me more confident in my ability to evaluate the important information from these documents. Additionally, I had never worked with external I/O with an FPGA. This involved going beyond what I learned in 240/341. Similarly, we had to implement communication protocols at a lower level than using something like an Arduino library. This involved a lot of scrolling through the Internet on various forums and FPGA hobbyist blogs, as well as comparing Arduino library code to existing RTL implementations.

Nancy’s Status Report for 4/12

The past two weeks, Amelia and I have made good progress on the RTL. We currently have a working implementation of the rotary encoder, which can change the number displayed on the on-board 7 segment displays, but we do have some strange jumping issues when we try to implement it by scrolling through the alphabet, since there is some unexpected behavior on reset. Additionally, we spent the majority of our time working on the external seven segment display that uses the MAX7219 chip. We had a lot of trial and error trying to adapt Arduino library code and existing RTL code (that was in VHDL, not Verilog) to work in Verilog. We used an Arduino to verify that the display itself worked, but after a lot of debugging, we successfully displayed a message early this week!

Later this week, Amelia and I worked on expanding our implementation of the variable rotor settings. For our demo, we only had users change the rotor starting setting (A-Z), but still hardcoded the rotor type (1-5) and ring starting setting (A-Z). On Friday, we spent most of the day implementing this and got all of the settings to display on the external 7 segment display! These settings could all be changed using the switches and buttons on the DE-10 and we verified that changing these settings reflected in accurate encryptions using an online Enigma simulator.

Now that the PCB has arrived, Amelia and I need to start wrapping up our RTL. This week, we will work on the shift registers for the lampboard, which should be pretty simple, and we will debug the rotary encoder implementation too. This will keep us on schedule.

As Amelia and I have been working on the RTL, it was very helpful to verify the individual components along the way. This made integrating them much easier. For example, we first got the rotor settings to display on the on-board DE-10. Using the on-board I/O (buttons and switches), we verified that the rotor settings could be changed and that they were correct when compared to the original Enigma machine using an online simulator. This included focusing on edge cases like the wrap-arounds from Z-A and the transitions at the knockpoints, which cause the other rotors to rotate as well. We also individually tested that the 7 segment display worked, and then incorporated that with displaying the actual settings. We will continue to run these targeted tests around edge cases and plan on conducting user testing to see how people who are not familiar with the design will interact with it. We want to ensure that the encryption is always 100% correct.

Tanisha’s Status Report for 4/12

This past two weeks I worked on preparing for our interim demo, working on PCB manufacturing tasks and other odd items.

I ordered our stencil from OshStencil. I ran into a few issues with trying to resize our stencil as it was charging us for a lot of negative space even though I didn’t need those extra sq inches. However, I was able to order it and it arrived successfully.

Since our stencil hadn’t arrived for the earlier part of this week, I worked on writing encodings to our Micro SD cards and making sure everything was formatted correctly, and running storage tests. I pivoted from using H2testw to f3 testing so I would be able to check storage sizes as well as corrupt disks.

I also started working on our Final report – specifically the PCB section as that is solely my responsibility as well as updating the Ethics session of our paper based on our Ethics lecture notes and previous status reports.

On Friday the PCB arrived (yay!). I immediately fabricated the resistors in the Fab Lab in Techspark and on Saturday I hand soldered the LEDs, 7 segment display, shift registers, FPGA header and the SD card reader and its right angled header. This comprises the majority of our PTH components.

I ran into slight issues as I had planned to desolder the right angled headers that came with the rotary encoder for a clean look and to balance the center of gravity for our users. However, that was proving tricky and I didn’t want to mess with the rest of the board as we got the last 2 rotary encoders in stock and hence have no spares. Due to this, I tried to source right angled female headers on campus but ended up just ordering some. Once these arrive, I can solder the rotary encoder and with that the PCB fabrication would be complete. I have attached a picture of the current state of the PCB to this status report.

This week I plan to run more continuity tests (I did small modular testing as I soldered the PTH components), ensuring all parts are soldered on with sufficient connection and no shorts. For verification I will double check multimeter output against the design schematic and ensure all works as expected (grounds, vcc, shorts etc).

I also plan to work with our Verilog team to on integrating our PCB and FPGA successfully. This should leave plenty of time to have everything working successfully by the end of the semester.

Amelia’s Status Report for 3/29

As mentioned last week, I had some challenges integrating the PS2 protocol with the encryption modules. I spent a considerable amount of time at the beginning of the week fixing these issues and getting the code to synthesize on the DE10. The goal of this integration was to have a key pressed on the PS2 keyboard be encrypted through the Enigma encryption algorithm and to display both the plaintext letter and ciphertext letter on seven segment displays on the FPGA. I faced numerous challenges, the majority dealing with the press and release of the PS2 key.

After debugging, I realized that each letter was being double encrypted, so when a single button was pressed, it was encrypted twice. However, on Friday, Nancy and I spent 12 hours in 1305 figuring out the issue. The main culprit was the letter was being sent twice via PS2 through the “make” and “break” codes. While we had been suspicious the break code might be the issue, we didn’t realize it was the root cause of our issues until we took a slo mo video of the seven segment display and figured out that “F0” was being flashed after release. We wrote another FSM to track the history of a key press and release and use that value in encryption. By Friday night, we had successfully integrated the PS2 keyboard with the Enigma encryption.

On Saturday (today), we spent the day in 1305 variable rotor starting settings via switches to allow the user to change the rotor starting settings. Nancy explains the issues we faced with this in her status report. By Saturday night, we had successfully added variable rotor starting settings to our integrated PS2 and Enigma encryption system and we are demo ready! Here is a video of us encrypting “Hello” from plaintext to ciphertext and back to plaintext — demonstrating how symmetric cryptography works!

Next week, Nancy and I plan on testing and integrating the rotary encoder and MAX 7-segment display with the rest of our system so we are ready to hit the ground running when our custom PCB comes in!

Nancy’s Status Report for 3/29

In the beginning of the week, Tanisha and I worked on routing the PCB, especially figuring out the routing around the shift registers and how best to organize the many LEDs/resistors to minimize trace complexity. Once she had finished the rest of the routing, we also worked to fix an issue with the 3.3V/GND pours on Fusion and I reviewed the layout one more time before Tanisha placed the order.

In the later half of the week, Amelia & I spent a lot of time in 1305 debugging the integration of the encryption modules with some basic GPIO using the buttons, switches, and 7-segment displays that already exist on the DE-10. This is a good stepping stone towards incorporating the GPIO from our PCB and also gives us a good way of demonstrating our progress in our interim demo.

More specifically, we initially had issues with the encryption itself being incorrect. One issue is that our 3rd rotor needed to be “rotated” once before encryption, so it was as if the first rotor started on Z when we expected it to be on A. While this was a quick fix, we also realized that we were overlooking the break code component of the PS/2 protocol. By incorporating an FSM that could alert our other modules of when a key was released (and therefore the break code was sent), we were able to fix our encryption and have the cryptographically correct result display when (and only when) the key was being held down on our external keyboard. This mimics how the lampboard will light up only when a key is pressed. Next, we moved onto incorporating more I/O. For the demonstration, we decided to make the starting rotor position for all 3 rotors variable, where switches would select which rotor to rotate and a button would allow you to cycle through the alphabet. After a day spent debugging this implementation, we successfully translated “Hello” to ciphertext and back on Saturday night! Here is a video of it working.

Next week, Amelia and I plan to work on capstone in the first half of the week before Carnival. We aim to incorporate the rotary encoder FSM that I wrote with our existing design and start on the I2C communication for the MAX 7-segment display. This will keep us on schedule since we want to have as little difficulties as possible incorporating the PCB by making sure the individual I/O components can work with our Verilog.