In the beginning of the week, I finalized the design presentation, especially making sure that our use case requirements were quantifiable and translated into quantifiable design requirements. Later, I worked on the design report, adding more to the introduction and use case requirements sections. Most of this was elaborating on how our use case and its social/economic/historical implications leads to our quantitative requirements.

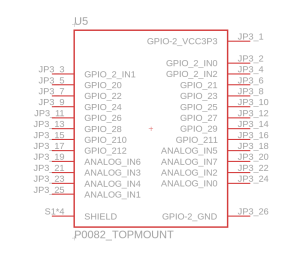

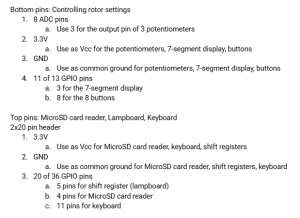

I also worked with Tanisha on finalizing our PCB schematic. While reading the De0-Nano datasheet, I saw that we had overlooked how the ADC pins are on the bottom of the FPGA, unlike the 2 2×20 GPIO pins. However, the ADC pins are also only accompanied by 13 GPIO pins, so it would not be possible to put all of our I/O on the bottom pins. So, I began exploring how to split up our PCB into 2, with the rotor functionality on the bottom pins where the potentiometers would be (which would need the ADC pins), and the lampboard/SD card/keyboard using the top pins. Additionally, I spent some time looking for the footprint for the FPGA, but I could only find a Fusion-compatible version for the bottom pins. This was a concern since we wanted the PCB to fit perfectly over the top pins on the FPGA and we want the spacing between the two 2×20 headers to be accurate. However, since we can move some functionality to the bottom pins, we only have to use one of the 2×20 headers, eliminating this concern.

Finally, I also researched into interfacing with the ADC and SD card reader through the FPGA. I found two Intel IP cores that work with Quartus that could be helpful — the ADC and SPI cores.

In order to stay on schedule, Tanisha and I need to finalize the PCB schematic and layout before spring break, which will be a good amount of work but doable with us both. This week, I hope to finish this so we can order the PCB over break, and also continue to edit the design report once we receive feedback on our presentation.