Personal tasks of this week:

Task: Circuit Simulation:

Definition: According the Sergey’s thesis, the theoretical circuit primitives were found to model the mathematical constraint. However, the circuits need to be modified to realize the theoretical circuit, as it contains ideal circuits that don’t exist in the real world.

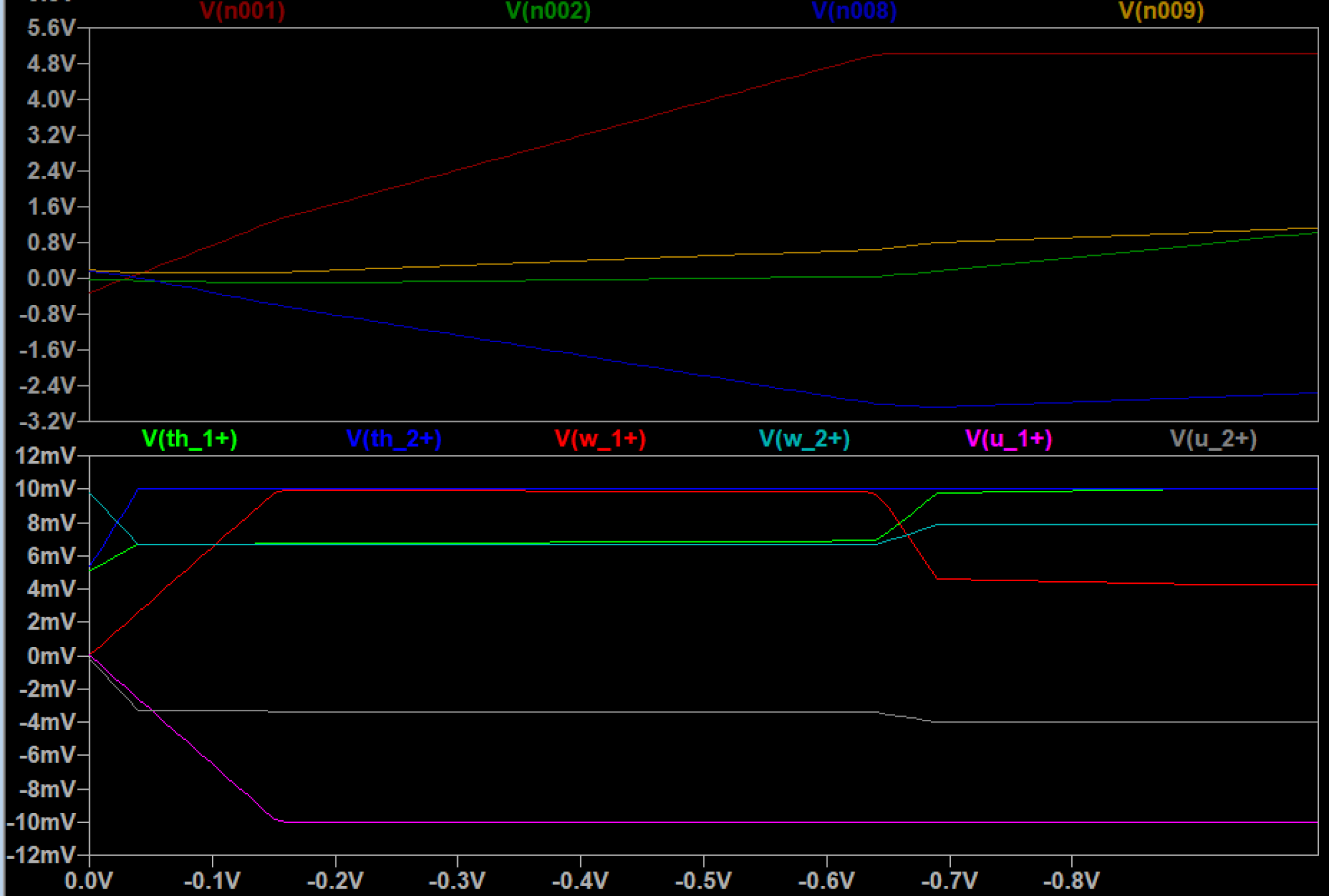

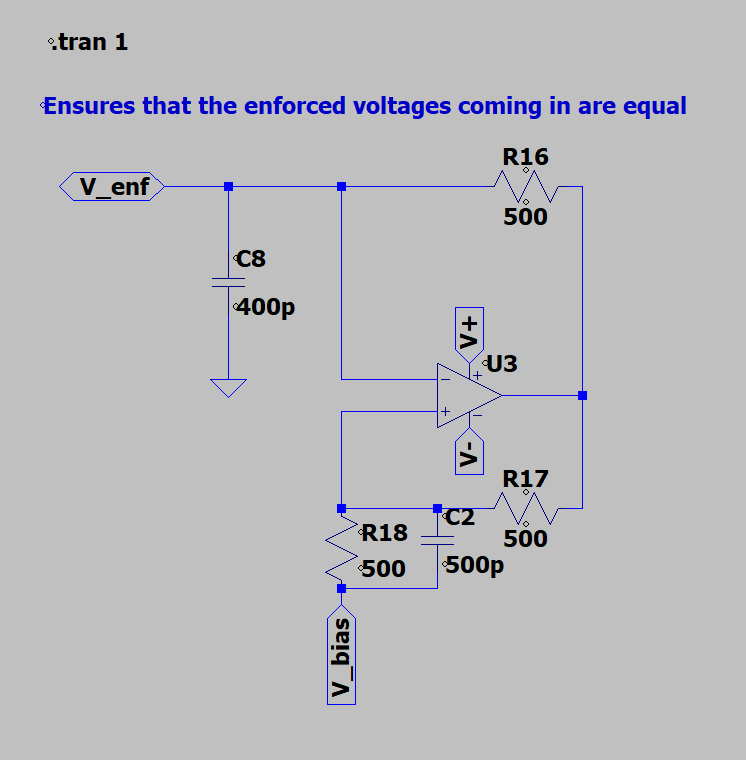

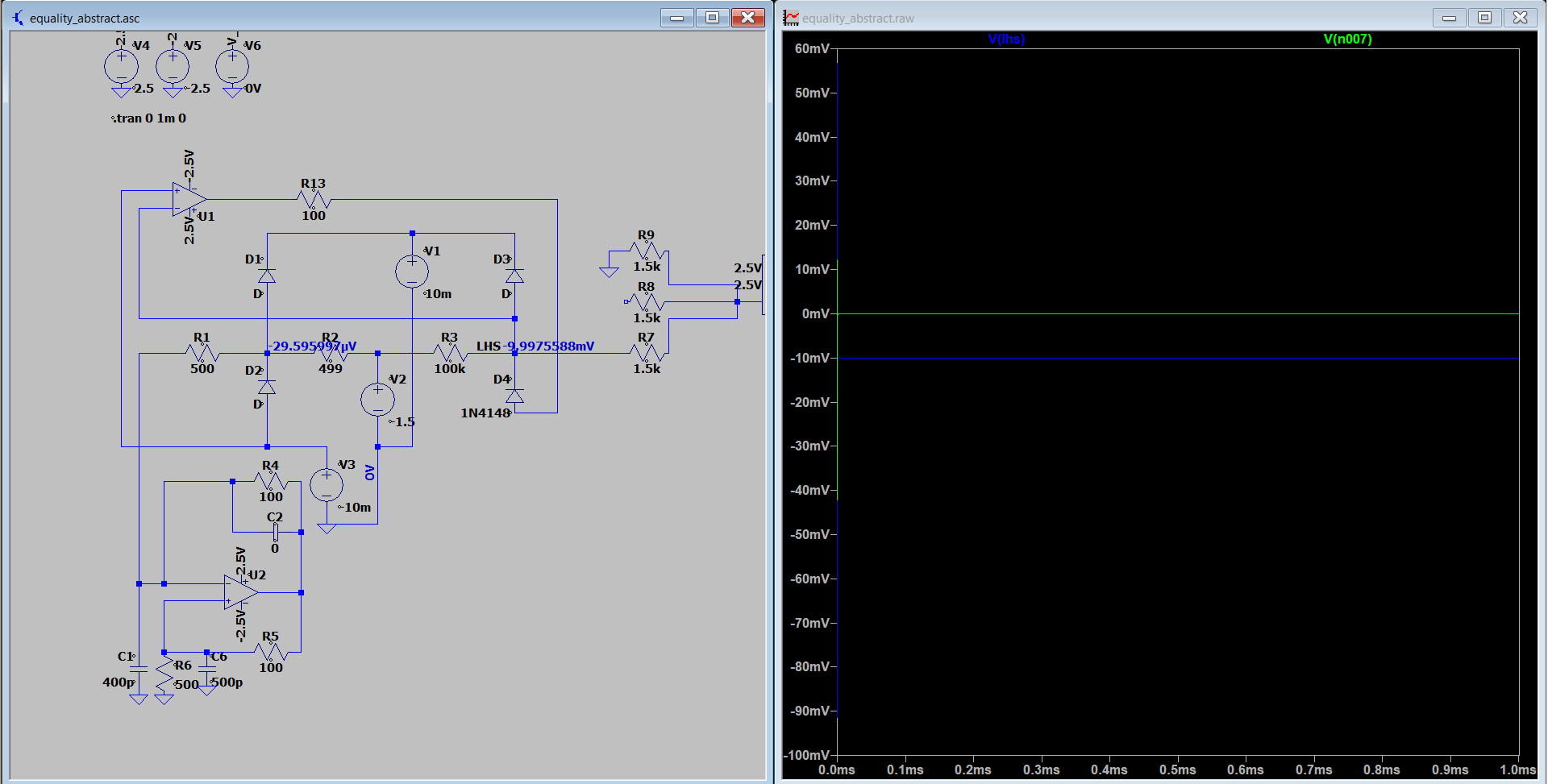

Completion: The task is completed. Analyzing the issues from Sergey’s thesis from last week, we were able to solve all of the issues we were facing. In regards to the equality constraint, we realized that the theoretical formulation of the constraint was correct, but did not take into account that the op-amp rail voltages are not infinite :/ As a result, if the voltages in the realized simulation end up maxing out at the rails, the circuit would continue to oscillate and never converge. To fix this, we realized that we can scale down our operating voltage from -100 mV – 100 mV, which was used my Sergey, to -10mV – 10mV. As a result, in our simulations, we can observe that the voltages properly converge. All of the simulations now are verified using the models of the finalized BOM.

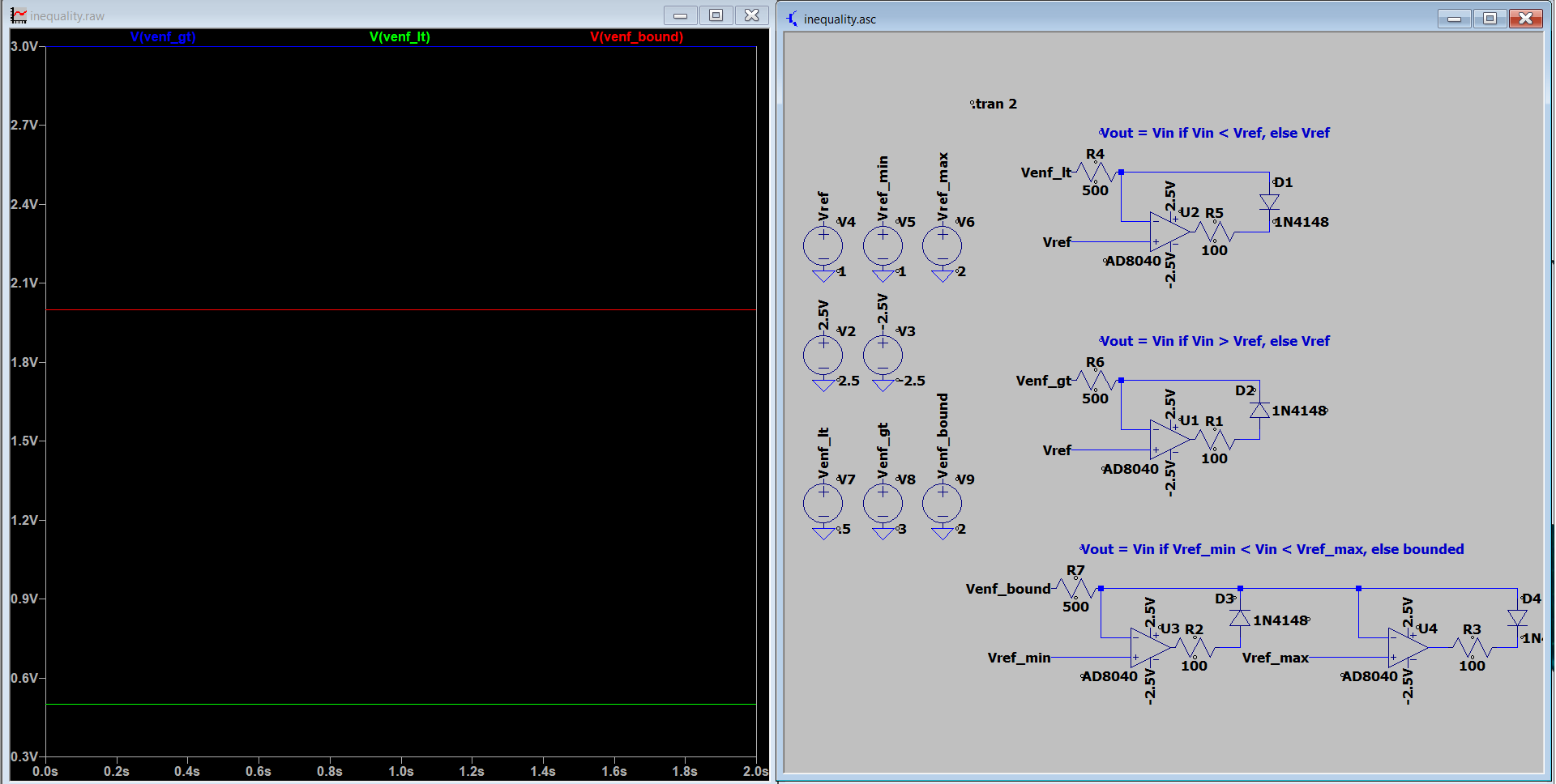

Furthermore, the constraints were abstracted into components in LTSpice to make simulation much simpler and less prone to errors.

The inequality constraints were based on an op-amp clamp. Simply changing the direction of the diode will change the direction of the op-amp. Chaining two of them together can create a bounded clamp.

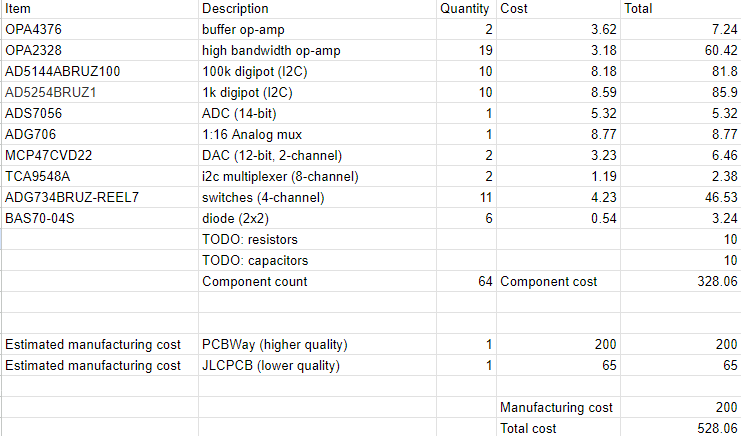

After slightly descoping the project, here is the finalized BOM. Now, even when considering the more expensive, but reliable option, PCBWAY, we are within the allocated budget for the project.

Next Steps:

The next steps is to create full scale simulation of the optimization circuit using our currently verified and abstracted constraints. Considering that we have slightly descoped the optimization problem to ensure that the final demo will work, we are now on budget as well.

Overall progress assessment:

My progress is slightly behind-schedule, as we have resolved all of the current issues with the circuit, but because of that, are behind in the PCB design and fabrication.