Personal tasks of this week:

Task: Preliminary Circuit Simulation:

Definition: According the Sergey’s thesis, the theoretical circuit primitives were found to model the mathematical constraint. However, the circuits need to be modified to realize the theoretical circuit, as it contains ideal circuits that don’t exist in the real world.

Completion: The task is partially completed. Further research was done in order to finalize the components that would be used. In particular, a preliminary BOM of the PCB was created:

| Item | Description | Quantity | Cost | Total |

| OPA4376 | buffer op-amp | 4 | 3.62 | 14.48 |

| OPA2328 | high bandwidth op-amp | 26 | 3.18 | 82.68 |

| AD5144ABRUZ100 | 100k digipot (I2C) | 16 | 8.18 | 130.88 |

| AD5254BRUZ1 | 1k digipot (I2C) | 16 | 8.59 | 137.44 |

| ADS7056 | ADC (14-bit) | 1 | 5.32 | 5.32 |

| ADG732 | 1:32 Analog mux | 1 | 14.41 | 14.41 |

| MCP47CVD22 | DAC (12-bit, 2-channel) | 6 | 3.23 | 19.38 |

| TCA9548A | i2c multiplexer (8-channel) | 3 | 1.19 | 3.57 |

| ADG734BRUZ-REEL7 | switches (4-channel) | 19 | 4.23 | 80.37 |

| BAS70-04S | diode (2×2) | 8 | 0.54 | 4.32 |

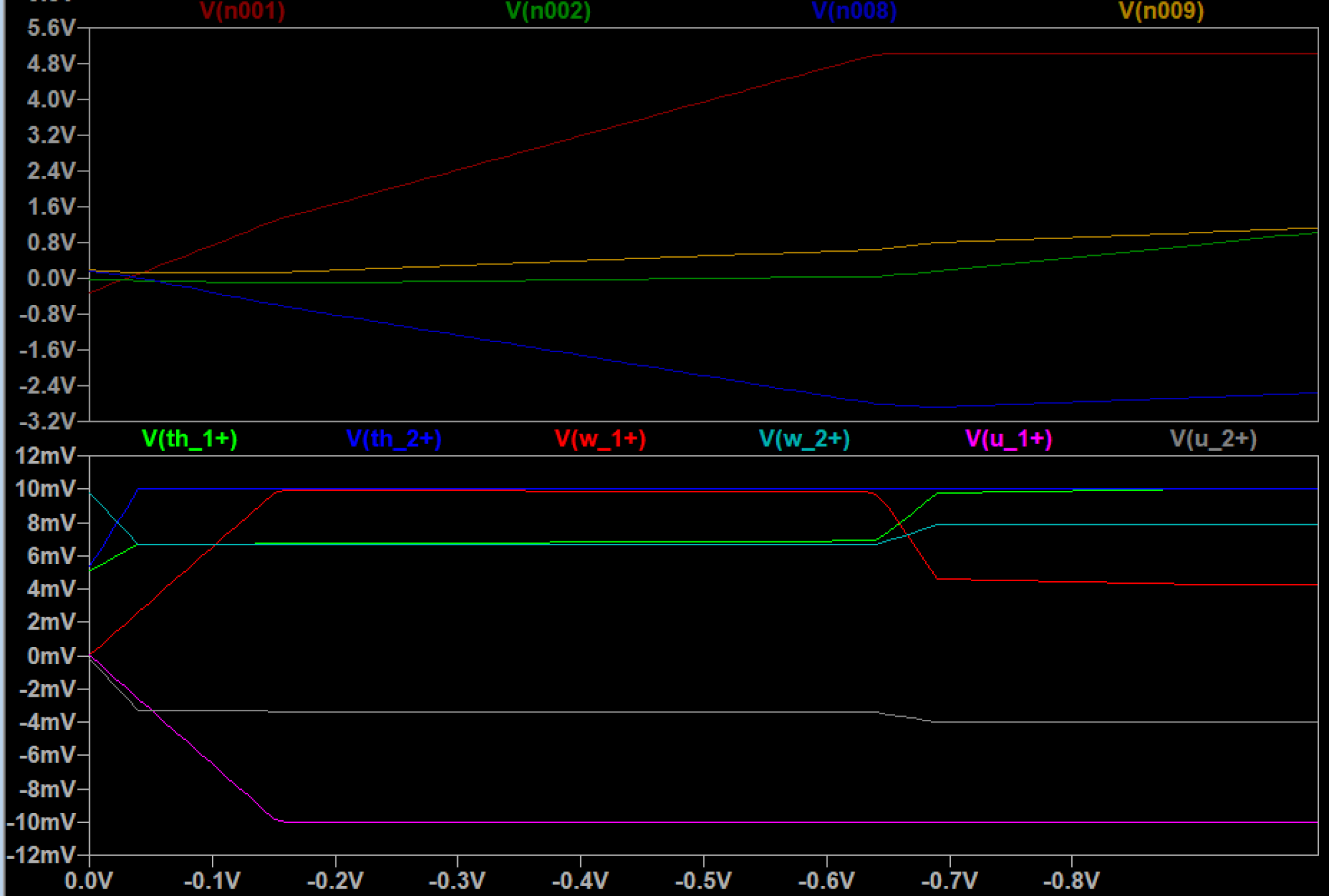

Furthermore, while we found significant issues with the realized formulation of Sergey’s thesis, we were able to create and simulate the realized constraints in LT Spice. The behavior of each constraint was verified and now only the simple optimization problem needs to be created.

Next Steps:

The next steps are to first create and verify the simple optimization problem, and then scale to the full problem once we are able to resolve the issues and concerns we have with Sergey’s thesis.

Overall progress assessment:

My progress is slightly behind-schedule, as we needed to address issues regarding Sergey’s thesis, but we have resolved the majority of issues regarding it.