- Personal Accomplishments

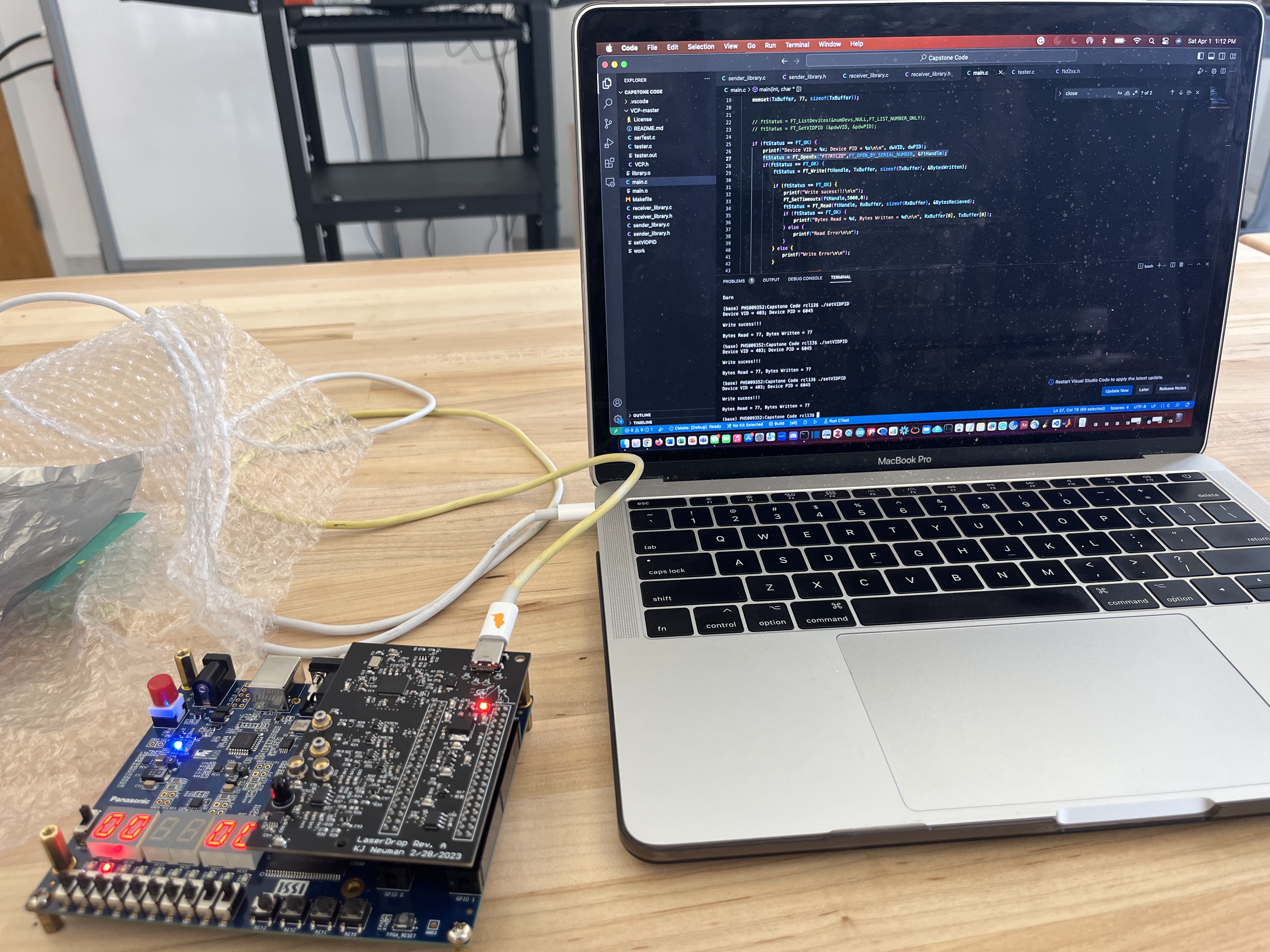

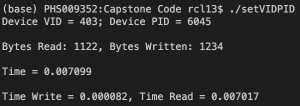

- I was finally able to interface properly with the FTDI chip and FPGA board using an echo program to write bytes to the FPGA. Instead of interfacing through a VCP, we will be using the D2XX library. It seems that read times are slow relative to write times, so this issue needs to be addressed. However, I can now begin to write the full software pipeline for the sender/receiver path. Pictures of the echo and timing are below.

- Anju and I also updated the protocol as the read speeds would slow down the transmission time, and we would like to minimize reads as much as possible. We will return to a previous protocol where all packets will be sent at once, and an error queue will be created with packets that did not pass Hamming decoding and inspection. I will need to implement a priority queue to properly reconstruct packets. Instead of doing these in parallel however, because we will only have one green laser per device, due to the IR laser being rendered unusable, we will not parallelize the processes of the sender sending packets and the receiver requesting errored packets. We will instead wait until all packets are sent, and then re-request all packets from the error queue.

- Additionally, we will increase the tag ID to 4 bytes to avoid the complication we had before of modular arithmetic when packets reached the highest representable byte number (We do not expect a file to be of size 2^42 Bytes or 4.4 TB which would be the size needed to cause tag ID modular arithmetic).

- We will also increase packet sizes to 1 kB (1024 Bytes) to speed up delivery. This will mean that I have to update my Hamming encoding code for an increased number of Hamming bits.

- Schedule

- My schedule is behind now due to all the discoveries and limitations encountered. With that being said, with demo day approaching on Wednesday, I will focus all my attention to write out all this software and test with hardware now that many design choices have been finalized. I don’t expect too many more curveballs, so I can fully commit to the current design ideas. I plan to have a fully functioning Hamming encoding demonstration for Wednesday, and possibly the pipeline to send bytes from one device to another via laser provided that Anju can finish her script for controlling the FPGA.

- Deliverables for Next Week

- Readjust my Hamming encoding code for the different packet design and increased size.

- New test cases

- Begin fully implementing software that integrates library code Iinto sender and receiver- code for the device.

Anju Ito, Roger Lacson, and KJ Newman