# To the 60's and Back

A modern take on the Apollo Guidance Computer (AGC)

Group E0: Christopher Bernard, Donovan Gionis and Jae Woong Choi

## Use Case

The Customer requires a device to control and handle their rocket. They want:

- An *efficient*, *improved* flight computer to calculate the future spacecraft trajectory (basic Newtonian orbital mechanics).

- A computer that keeps track of spacecraft status and sensors, such as *mission time elapsed, battery power level, current power usage, warning*, etc.

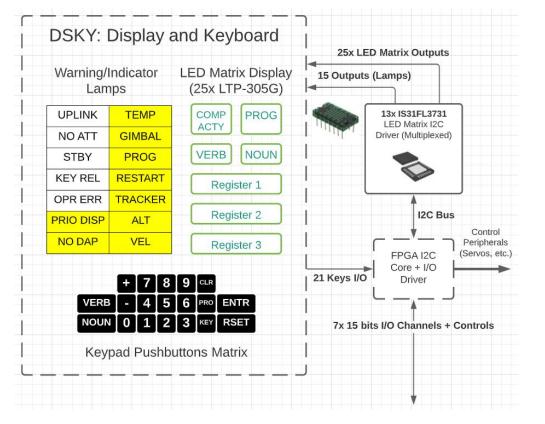

- A compact reliable display and keyboard interface (DSKY) to interact with the computer

- To use an I/O focused ISA that is proven to have work for manned space travel

Areas covered: Hardware Systems, Software Systems

### **Use Case Requirements**

- Given our mission time we should be able to calculate and write to the given I/O register for current battery level, distance from earth and moon within **1ms**. It should also be able to be accessed through DSKY.

- The DSKY will contain **compact LED displays** (capable of displaying seven segment) and **control lights** to display important information. A **tactile keypad** will be provided for input

- Improved Frequency 1.1Mhz->50Mhz. Condensed ISA 37->21 instructions, Decreased Weight/size 70lbs-> 3.5lbs.

- Each instruction we implement will pass a specialized test for that instruction in simulation

Technical Challenges: Verification, Assembler, Reduced ISA

- How will we **verify** that our processor meets the **requirements**?

- How will we set up an infrastructure that is capable of testing our processor?

- An **assembler** is needed to run **test/demo** programs.

- How can we simplify the original ISA while retaining its defining features?

## Our ISA

| Format | Operation                                          | Format   | Operation                                          |

|--------|----------------------------------------------------|----------|----------------------------------------------------|

| ADD K  | A = A + [K]                                        | BZF K    | If A = 0; PC = [K]<br>Else PC = PC + 1             |

| ADS K  | [K] = A + [K]<br>A = A + [K]                       | BZMF K   | If A <= 0; PC = [K]<br>Else PC = PC + 1            |

| AUG K  | If [K} >= +0; [K] = [K] + 1<br>Else; [K] = [K] - 1 | RETURN   | PC = Q                                             |

| СОМ    | A = ~A                                             | READ KC  | A = {KC}; Note {} means read from I/O channel      |

| CS K   | A = -[K]                                           | WRITE KC | {KC} = A                                           |

| DIM K  | If [K} >= +0; [K] = [K] + 1<br>Else; [K] = [K] - 1 | NOOP     | Nothing                                            |

| DOUBLE | A = A + A                                          | INDEX K  | Next instruction in memory is executed differently |

| INCR K | [K] = [K] + 1                                      | EXTEND   | Next instruction uses extra code to interpret      |

| MASK K | A = A & [K]                                        | NOOP     | Nothing                                            |

| SUK    | A = A - [K]                                        | TS K     | [K] = A                                            |

|        |                                                    | CA K     | A = [K]                                            |

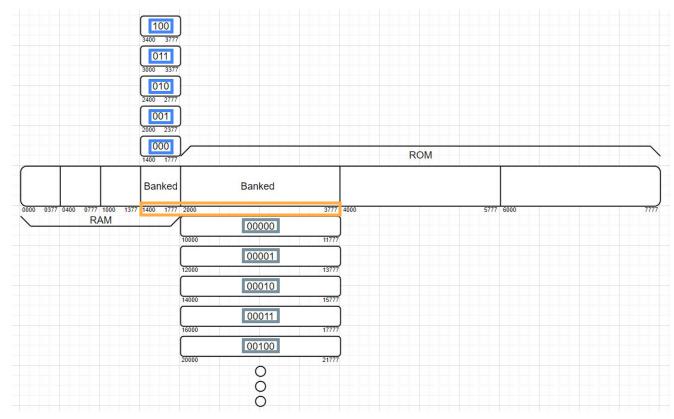

## Memory Map

These addresses must be translated prior to memory access.

Translation based on...

3 Erasable Bank (EB) selection bits for banked RAM

5 Fixed Bank (FB) selection bits for banked ROM

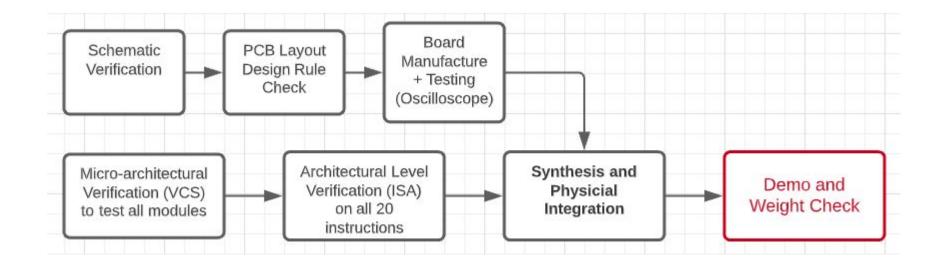

### **Technical Challenges** Hardware Development & Integration

- How do we design a DSKY PCB to meet our requirements? Which components?

- Development of the DSKY interface will require a customized PCB: requires *component selection*, *schematic design*, *PCB layout*, and *PCB assembly*.

- Take into account component **shortage**, PCB board shipments, etc. to minimize **risk**.

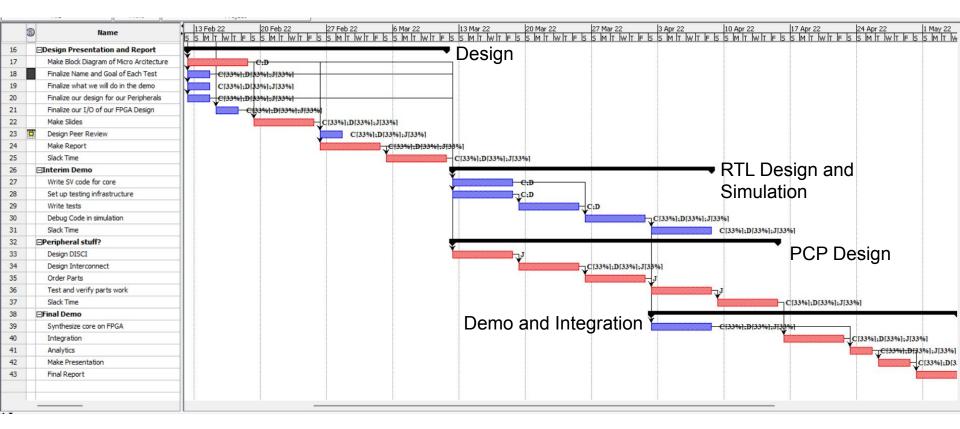

- **Time allotment**: Hardware development, DE10 board setup will need to happen **parallel** with architecture development for time.

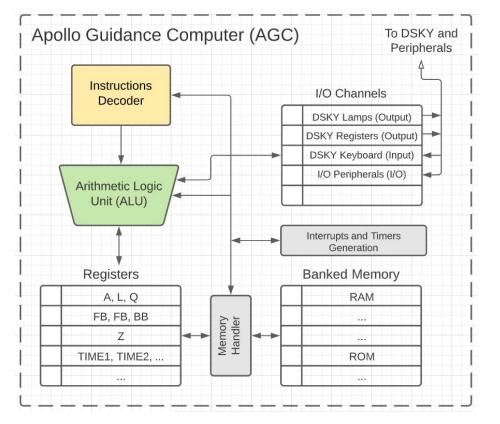

# Solution Approach (System)

- DSKY is the primary user interface for the AGC

- Design a custom PCB containing LED indicators, LED matrix displays, and keypad

- FPGA will be interfacing the displays/indicators through an I2C bus for minimal I/O usage

- The board will be assembled manually using TechSpark equipment

- All parts chosen are confirmed in stock in Digikey/Amazon (500+ stock)

## Solution Approach (CPU)

- The AGC architecture will be implemented with Intel (Altera)

FPGA in SystemVerilog. Current candidate is **DE10 with SoC**.

- With the help of SoC, the AGC will have accessed to simulated mission data

- Custom AGC assembly routines based on Apollo Luminary 99 programs will be written and run on our hardware to demo functionality

#### **Testing and Verification Metrics**

#### Schedule and Division of Labour

## Conclusion

- AGC Architecture

- Purpose-built for **space travel**

- Modern Redesign

- Use EDA, synthesis tools, miniaturized IC form factor

- Vastly **smaller** package, **faster** performance

- Target Commercial Space Travel

- Recent **surge** in national interest

- Efforts to reach Mars