# Bluetooth Audio Rejiggering Instrument (BARI)

Adam Quinn, Sam Rainey, Xingran Du (Group D0)

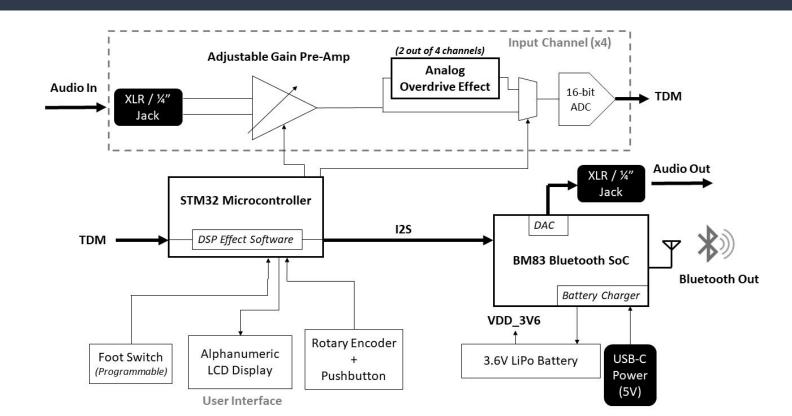

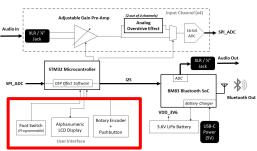

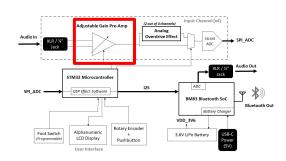

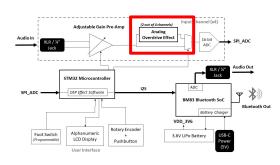

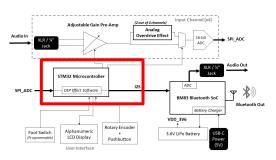

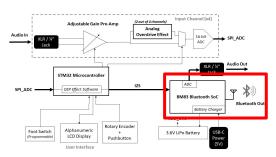

## Block Diagram

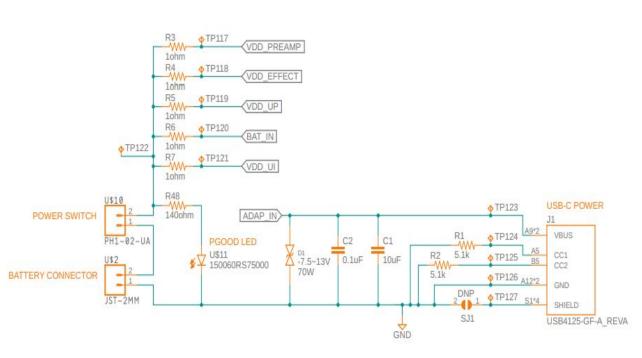

### Power Module

#### **INTERFACES**

VDD out to all five modules. Battery, USB-C Connector

#### **IMPLEMENTATION**

Full custom design

#### **TESTING**

Battery Lifecycle Test System Power Consumption Test

### User Interface Module

#### **INTERFACES**

Control to and from Microcontroller

#### **IMPLEMENTATION**

PEC12R Rotary Encoder + Button NHD 128x64 LCD Lovermusic SPDT Footswitch

#### **TESTING**

User Interface Latency Test Ease-of-Use Test

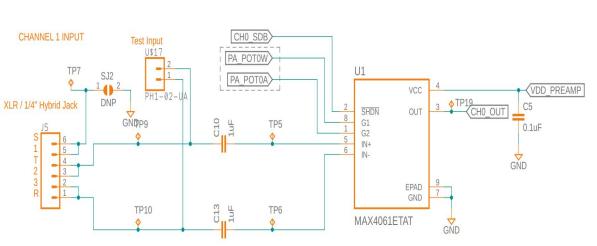

## Pre-Amplifier

#### **INTERFACES:**

Audio in from XLR/ ¼" Jack Audio out to Analog Effect Control from Microcontroller

#### **IMPLEMENTATION**

MAX4061

#### **TESTING**

Pre-Amplifier Functional Test (Input, Output, Gain Flatness, Distortion)

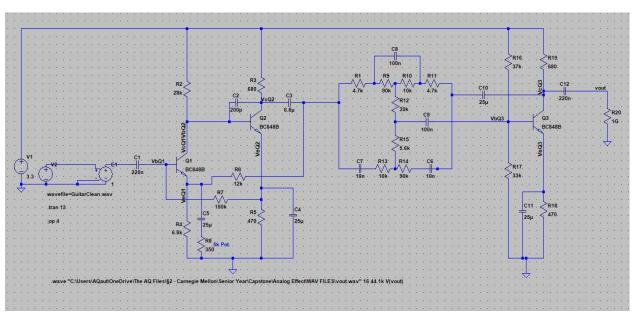

## Analog Overdrive Effect

#### **INTERFACES:**

Audio in from Pre-Amp Audio out to ADC Control from Microcontroller

#### **IMPLEMENTATION**

Based on Colorsound Overdriver factory schematic, redesigned for 3V3.

#### **TESTING**

Analog Effect SPICE Verification Test

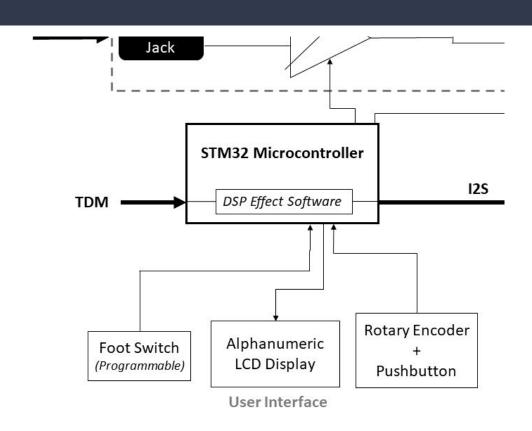

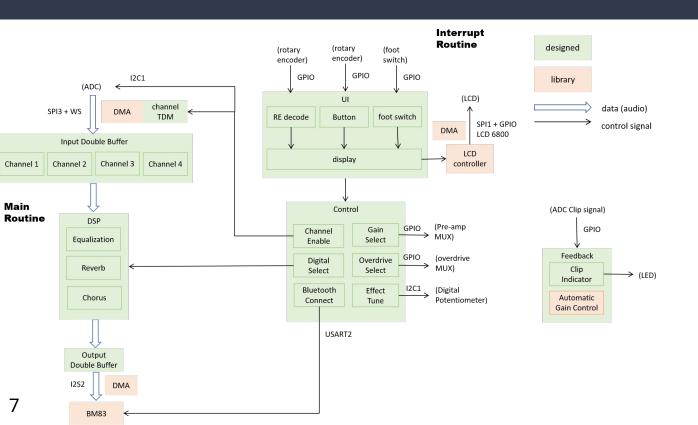

### Microcontroller

#### **INTERFACES:**

16-bit 4-channel ADC input through SPI (with Time-division Multiplexing)

Single channel output through I2S

GPIO for UI & channel select

I2C for Digipot and ADC control

LCD control via SPI

UART for Bluetooth control

IMPLEMENTATION

Separate data flow from central flow

Separate data flow from control flow

### Microcontroller Kernel

#### **IMPLEMENTATION:**

Kernel & Interrupt routines + Library code for common interfaces

#### **TESTING:**

Comm Protocol Bringup Procedure Per-Peripheral Unit Test Integrated w/ other system functional tests

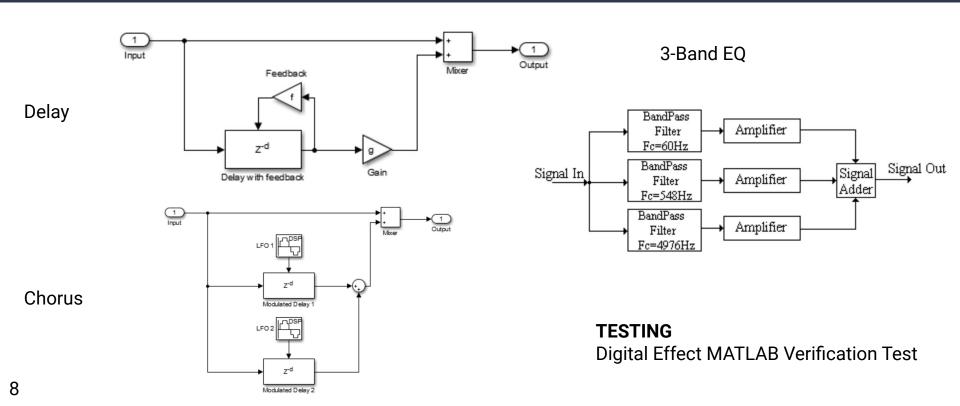

## DSP Algorithms

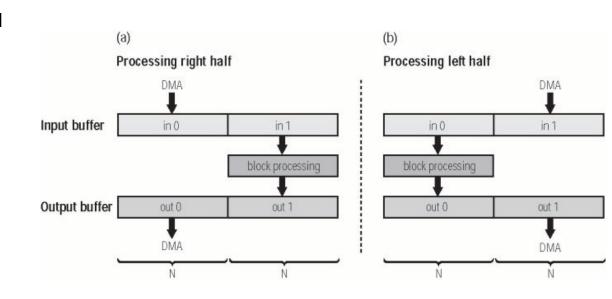

## DSP Implementation

**Specs:** 16-bit depth, 44.1kHz sampling rate, mono

Total SRAM: 190.7KB of 192KB

Double Input Buffer (4 inputs): 4KB total

Processing Space: 1.5KB

Previous Input Storage: 17.2KB Previous Output Storage: 1.6KB Wet Delay Line Storage: 165.4KB

Double Output Buffer (1 output): 1KB

Total Flash: 43.1KB of 1MB

Filter Coefficients (Flash): 39.1KB

Wavetable (Flash): 4KB

Minimum Latency: 2.9ms to 11.6ms

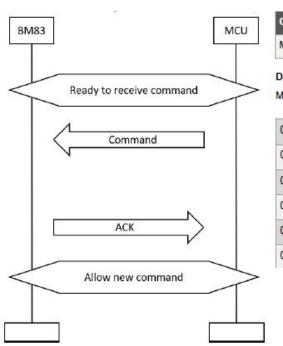

## Bluetooth Module (BM83)

| Command    | Op Code | Command Parameters      |  |  |

|------------|---------|-------------------------|--|--|

| MMI_Action | 0x02    | data_base_index, action |  |  |

#### Description:

MCU can send proper command to complete different kinds of action.

| 0x56 | Reset some EEPROM setting to default setting |

|------|----------------------------------------------|

| 0x57 | Force speaker gain toggle                    |

| 0x58 | Toggle button indication                     |

| 0x5D | Fast enter pairing mode (from non-off mode)  |

| 0x5E | Switch power OFF                             |

| 0x5F | Disable LED                                  |

#### **INTERFACES:**

I2S audio input, BLE output UART command input IMPLEMENTATION

Based on supplied library code and UART command set

#### **TESTING**

Bluetooth Range Test

## Schedule and Task Breakdown

|         | 1-Mar        | 8-Mar                     | 15-Mar          | 22-Mar          | 29-Mar         | 5-Apr            | 12-Apr          | 19-Apr | 26-Apr |

|---------|--------------|---------------------------|-----------------|-----------------|----------------|------------------|-----------------|--------|--------|

| Adam    | Rev 1 Layout |                           |                 |                 |                |                  | i               |        |        |

|         |              | Mechanical Desi           | ign             | _               |                |                  | İ               |        | F      |

|         |              |                           |                 | Rev 1 TEST      |                |                  |                 |        | 1      |

|         |              |                           |                 | Rev 2 Schem.    |                |                  | i               | S      | N      |

|         |              |                           |                 |                 | Hardware Imple | mentation        |                 | L      | Α      |

|         |              |                           |                 |                 |                |                  | HW Stress Test  | Α      | L      |

| Sam     | MATLAB Effec | t Prototypes              |                 |                 | Ì              |                  |                 | C      |        |

|         |              |                           | Embedded DSP I  | mplementation   |                |                  |                 | K      | Р      |

|         |              |                           |                 |                 | SW Unit Test   |                  |                 |        | R      |

|         |              | i                         |                 |                 |                | Full Signal Path | lest est        |        | E      |

|         |              | ļ                         |                 |                 |                | Interim Demo     |                 |        | S      |

| Xingran | SW Arch.     |                           |                 |                 |                |                  |                 |        | E      |

|         |              | SW Low-Level D            | evelopment      |                 |                |                  | i               |        | N      |

|         |              |                           |                 | SW Integration  | & Unit Test    |                  |                 |        | T      |

|         |              | 1                         |                 |                 |                | Full Signal Path | Гest            |        | Α      |

|         |              |                           |                 |                 | 1              | Interim Demo     |                 |        | T      |

|         |              |                           |                 |                 |                |                  |                 |        | 1      |

|         |              | ^ Order Rev 1             | ^ Design Report | Due             | :              |                  |                 |        | 0      |

| 1       |              | ^ Design Presentation Due |                 | ^ Rev 1 Arrives | ^ Order Rev 2  |                  | ^ Rev 2 Arrives |        | N      |

11