# Carnegie Mellon

## **Chess Teacher**

Team B4: Michael Cai, Joseph Chang, Jee Woong Choi

#### **Product Pitch**

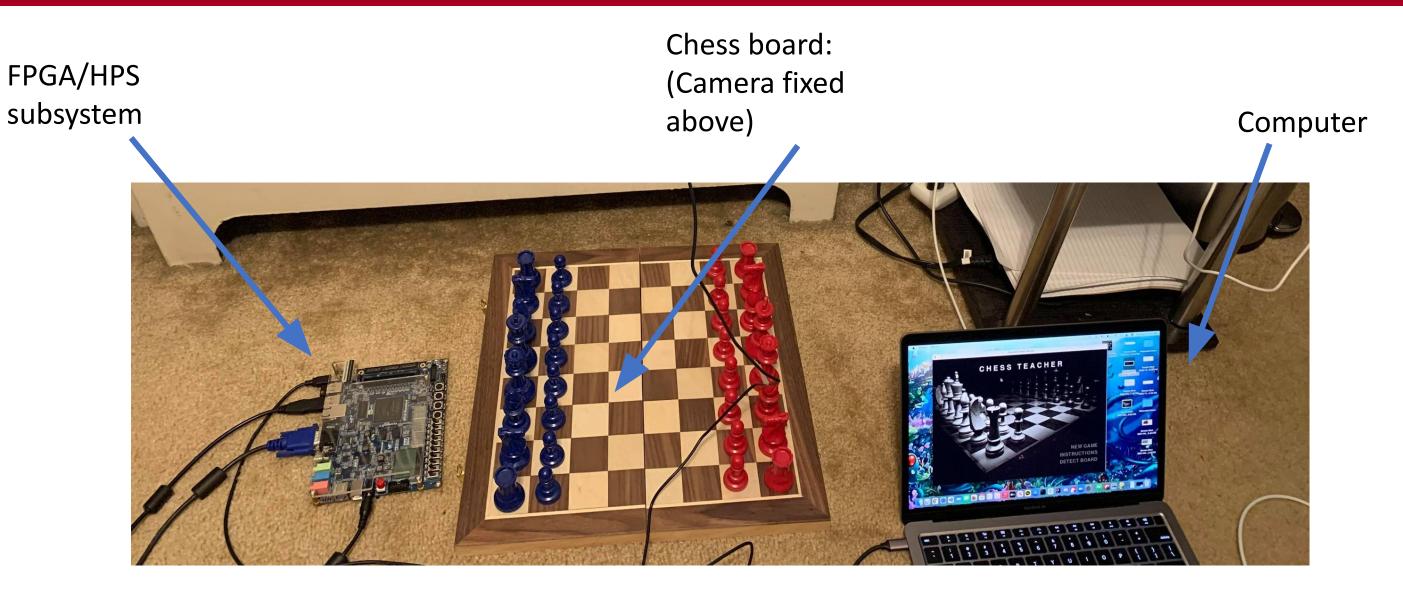

Chess Teacher is a system capable of teaching people how to play chess using artificial intelligence. What differentiates our product from the others is that it creates a more realistic environment by having physical pieces rather than playing on a computer. Our system can play chess against a human being on a real chessboard and also recommend moves to help them improve their performance. In this way, it allows for social distancing and a more economical approach than in-person chess tutoring. The system is built on a real chessboard with a camera to detect chess moves, and the computing is done using a computer and FPGA.

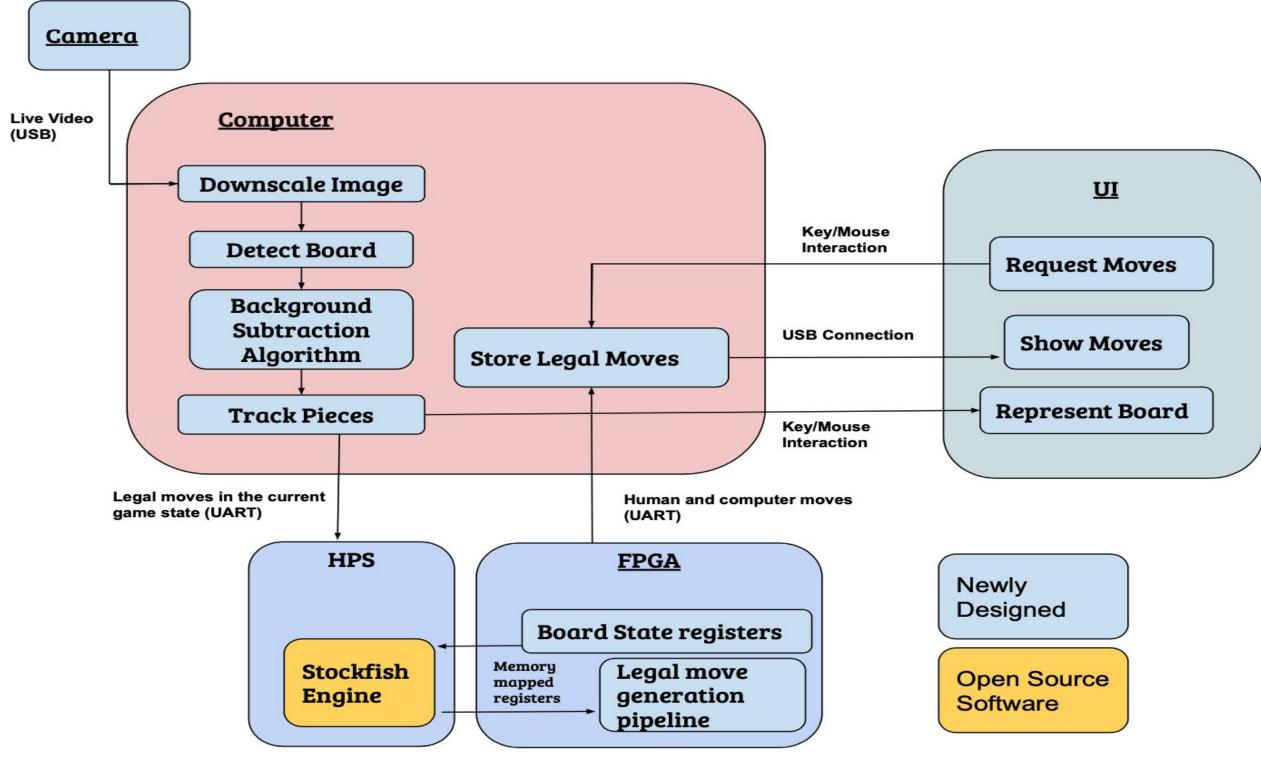

#### **System Architecture**

**Chess Teacher Block Diagram**

Figure 1: Block System Diagram

## **System Description**

Figure 2: Entire system setup

### **System Evaluation**

#### **Correctness Metrics**

| Requirement                             | Testing Strategy                                                                    | Metrics                                                   | Actual Output                              |

|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|

| Move detection                          | Software + Visual confirmation => 20 unique moves                                   | 99% accuracy in move detection & < 400 ms processing time | 20/20 Moves correctly detected             |

| FPGA legal move generation              | Hardware testbench (ensure correct legal moves generated) => 10 unique board states | 100% Correct                                              | 10/10 Board states correctly analyzed      |

| Communication between Computer and FPGA | Hardware testbench (analyze packets are sent correctly) => 15 unique packets        | Latency of < 1s & 100% data accuracy                      | 15/15 unique packets from PC to FPGA to PC |

| UI                                      | Visual confirmation of representing the board correctly => 20 unique moves          | 100% accuracy in representation of the board              | 20/20 Moves correctly represented          |