Risks

As mentioned in Deanyone’s status update, we are keeping close watch over the number of logic elements that are being consumed by the design. Our current prototypes are consuming 29K/115K logic elements on the lab boards, and require register retiming to be set in order to meet timing. It’s not clear how this maps to the ALMs used by the DE0-CV boards we intend to use in the final design, but those should be more efficient, rather than less, so using the Quartus logic element count for the lab FPGAs should be a reasonable upper-bound. While 29K logic elements does seem rather far from the 49K ALMs available on the DE0-CV boards, some of our more inefficient designs are as high as 40K logic elements. As a rule of thumb, the maximum upper bound of a utilization you can get off a FPGA is 80% due to routing inefficiencies. We are managing this risk by having continually updated hardware testbenches with reasonable usage, and optimizing the testbench and submodules when the usage spikes unreasonably high. This has only occurred once so far.

Another risk is our communication protocol, with the parts we are currently looking at, we estimate that there will be about 7.5 feet of cabling between boards. This is not unreasonably long, but could be significant in incurring bit-flips across the network. We are managing this by individually error correcting each data line. Further measures can be taken if it turns out our current protocol is unable to handle the error rate of the transmission medium.

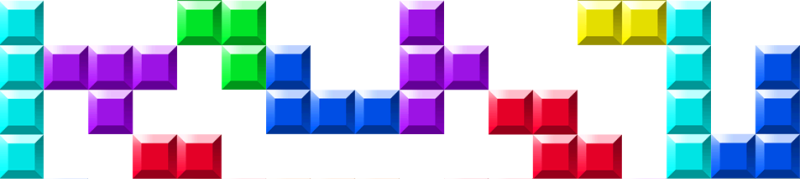

A strange issue we’ve run into is that of “pixel rain” (pictured below) appearing when we render the game board. Strangely, it is not appearing on dedicated VGA monitors, but the lab monitors with VGA capability that we’ve been using for testing seems to show the rain, which increases as we place more pieces.

![]()

Finally, there exists a supply risk regarding components such as headers and cables. If we require extra specific components down the line it is possible that it will be difficult to source them. We are mitigating this risk by ordering extras of our components in the hope that we will not need to order more later.

Changes to Design

So far, no major changes have been made to the requirements of the system. The only real change to overall system design thus far is the addition of an extra PCB for connecting the boards and peripherals, intended to make our lives easier when wiring everything together. See Alton’s individual update for more details on the new PCB.

Updated Schedule

Deanyone: No major updates to the schedule. The order in which I’m implementing features has been rearranged, but overall schedule is unchanged.

Eric: Similarly to Deanyone, no major updates. I am also implementing features in a slightly different order, but again the overall schedule is the same.

Alton: Progress on the music module has been a little faster than expected, and figuring out the finer details of the hardware has been a little slower. I’m still on schedule for both though.

Photos

Deanyone: Nothing major

Eric: See individual update

Alton: See individual update