Progress

Prior to the proposal presentation we had already made significant strides on the overall system design and game logic implementation. My focus has largely been on the networking aspect of our project – how we interface and communicate between two FPGAs running separate game instances. This week I finalized the details of the communication protocol, dubbed Tetris Synchronous Parallel INterface, or TSPIN. TSPIN is a synchronous, 4-bit parallel, stop and wait protocol with dedicated handshaking lines.

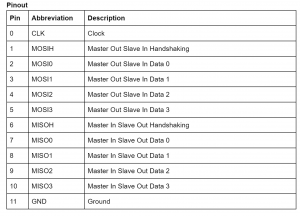

Since we are communicating over GPIO, we are limited in the rate of the clock we can send over it. Speaking with our TA who has worked with GPIO in the past, we determined that the worst case clock rate would be around 50kHz, although it is highly likely that we can go faster. I will check the actual viable clock rate next week since we now have access to the FPGA boards we will be using. With that worst-case clock rate, we get about 833 cycles per frame. The amount of information we need to transmit between boards adds up to 832 bits prior to encoding and synchronization, ideally occuring at least once per frame. As we are not IO limited in any capacity, I made the decision to make the protocol a parallel one to utilize our high available bandwidth. The final pinout is as follows:

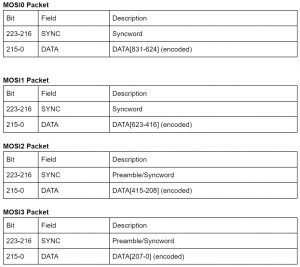

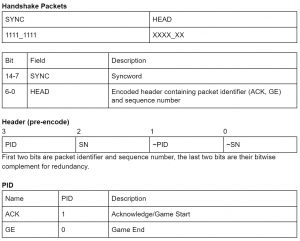

There are 4 data wires and one handshaking wire each way, along with clock and ground for a total of 12 wires. With the pinout decided, I finalized the layout and bit mappings of our packets, and reasoned about error correction methods. We expect error rate to be relatively low, and so decided on hamming encoding on each line along with additional redundancy for handshaking specifically.

From there I began implementation. After some discussion with Deanyone, we worked out the interface between the networking stack and game logic. Referencing my old 18-341 USB implementation, I designed the send and receive stacks, including FSMs and interfaces. The modules can be broken down as follows:

Packages

- NetworkPkg.sv

Send

- Sender.sv

- DataSender.sv

- HandshakeSender.sv

- SenderFSM.sv

- DataSenderFSM.sv

- HandshakeSenderFSM.sv

- HammingEncoderHnd.sv

- HammingEncoderData.sv

Receive

- Receiver.sv

- DataReceiver.sv

- HandshakeReceiver.sv

- ReceiverFSM.sv

- DataReceiverFSM.sv

- HandshakeReceiverFSM.sv

- HammingDecoderHnd.sv

- HammingDecoderData.sv

NetworkPkg defines constants and structures for the packets. Sender and Receiver are the pseudo-top level modules which interface with the game logic and instantiate the individual transmitters/receivers for each line, encoders and decoders, etc. This week I implemented and tested DataSender and DataReceiver, the modules responsible for sending/receiving data serially on a single wire. I also wrote up NetworkPkg and the interfaces for the other modules.

Schedule

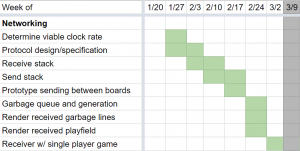

I am currently more or less on schedule, and hoping to have the bulk of the send/receive stack implemented and working in simulation by the end of next week. Finalizing the protocol took longer than anticipated due to needing instructor feedback, but I’ve caught back up. The ordering of implementation on the chart is a bit off from what I am actually doing, but the timing of completion should be the same.