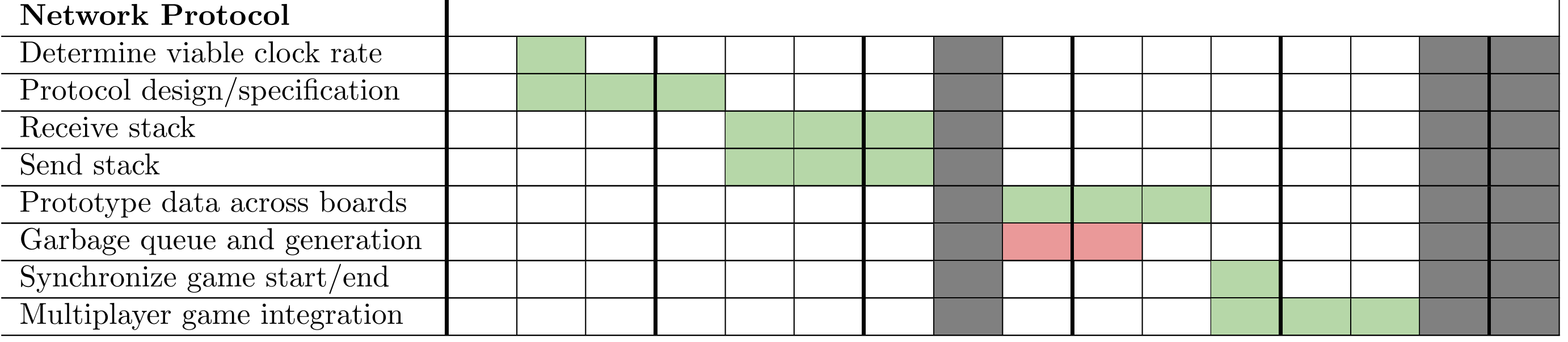

Progress on my end remains slow, but is gradually picking back up. As previously mentioned I’m quite behind at this point, so the schedule has been updated accordingly to push back network integration. See the updated chart at the bottom of this post.

The focus of this week was getting things set up and and trying to synthesize parts of the networking stack onto the DE2-115s. Setting up the boards and environment took a significant chunk of time, and compilation + synthesis on my personal computer is unfortunately rather slow. I also ran into a number of compilation issues with Quartus regarding unsupported language features, and compilation just crashing. Resolving these issues took a lot more time than I would have liked. It remains to be seen if I’ll need a logic analyzer for debugging purposes, but I’m hopeful we can avoid that situation given the amount of testing I’ve done in simulation. My current toolflow is not ideal compared to the lab setup, but it should function once I’ve finished ironing out the remaining issues.

With regards to risk management, the delays to the schedule and software/board pains have been the main challenges. Unless I run into significant issues successfully communicating across GPIO, the new setup is generally working and we should be able to accomplish our original goals. With those issues largely out of the way, the primary new risk from the COVID-19 situation is just a tighter timeline. To stay on track with the new schedule, I’m attempting to get the full sender + receiver on each board successfully communicating data back and forth for next week. The delays to integration are unfortunate, but hopefully we still have enough slack to make it work. Thankfully we have other subsystems working for the midpoint demo.

Updated chart: