# **NES emulation on FPGA**

Nikolai Lenney Diego Rodriguez Oscar Ramirez

## **Application Area**

- Faithfully recreate NES console on FPGA

- Play NES games with original controllers

- Support subset of NES games that use mapper-0 (NROM)

- Save game progress onto SD card

- Load game progress from SD card

### Solution Approach

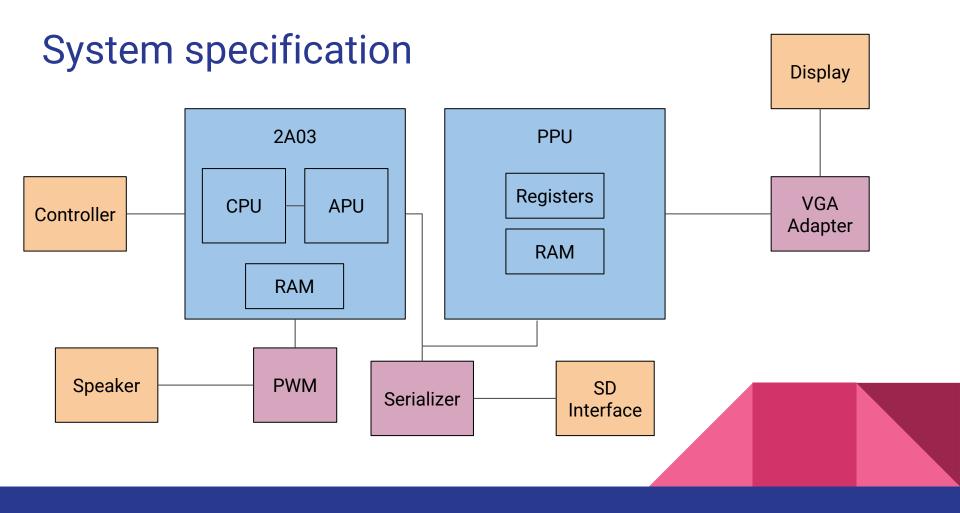

- Recreate the cycle accurate NES CPU, PPU, and APU

- Follow communication protocols for internal units

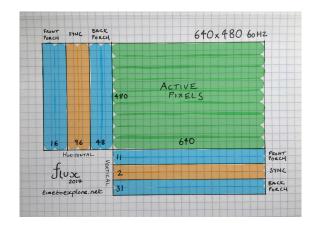

- Develop VGA module to display 640x480 resolution of NES games

- Purchase NES controllers, adapters, and 8-bit speaker

- Read controller inputs from FPGA GPIO pins

- Drive speaker without distortion

- Read and write data to SD card

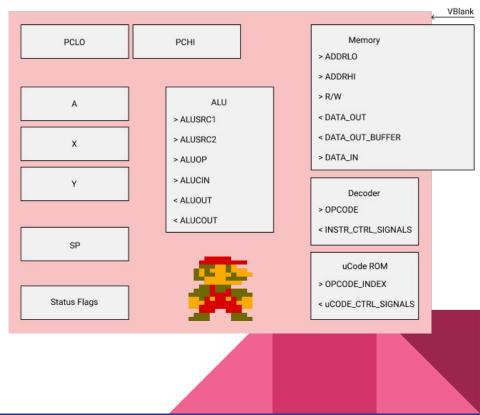

## System Specification - CPU

- Memory

- Memory maps to CPU RAM, Game

Cartridge ROM, Shared registers with

APU and PPU, and controllers

- Decoder

- Fetches a vector of control signals specific to a particular instruction, and independent of addressing mode

- uCode ROM

- Holds microinstructions for executing instructions of different addressing modes

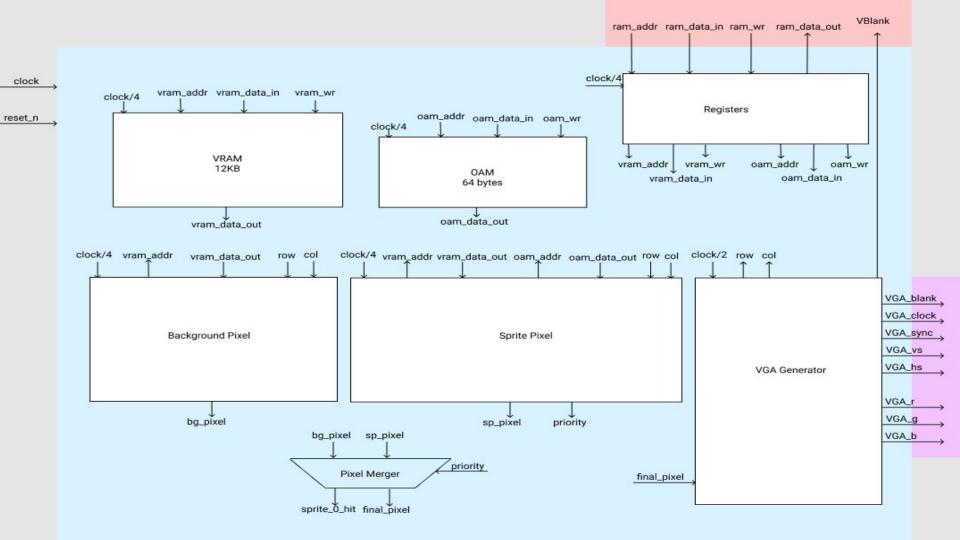

# System specification - PPU

- Rendering process:

- PPU renders 262 scanlines per frame, each scanline last for 341 clock cycles

- For every frame:

- -1 scanline: prefetch tile info for first two tiles

- 0-239 scanline: render background and sprite

- 240 scanline: idle scanline

- 241-260 scanline: VBlank lines, CPU can access VRAM

- For every visible scanline:

- 0 cycle: idle cycle

- 1-256 cycle: visible pixels

- output pixels based on VRAM

- prefetch next tile's

- sprite evaluation for next scanline

- 257-340: prefetch tile data for next line's first two tiles

# System specification - PPU

- Background pixel module:

- pixel color is determined by a combination of attributes in VRAM

- cache attributes for 2 tiles lines in registers, fetch new tile line every 8 cycles

- based on the first tile line, output the appropriate color

- during HSYNC prefetch first 2 tile for next scanline

- Sprite pixel module:

- pixel color is determined by OAM (object attribute memory) and VRAM

- use a Temp OAM to hold a max of 8 sprites for current scanline

- if current row and col are within range of sprite output pixel color

- during HSYNC do a linear search of OAM to fill the temp OAM with sprites in next scanline

- Pixel merger:

- based on the sprite's priority determine if background pixel or sprite pixel goes in foreground

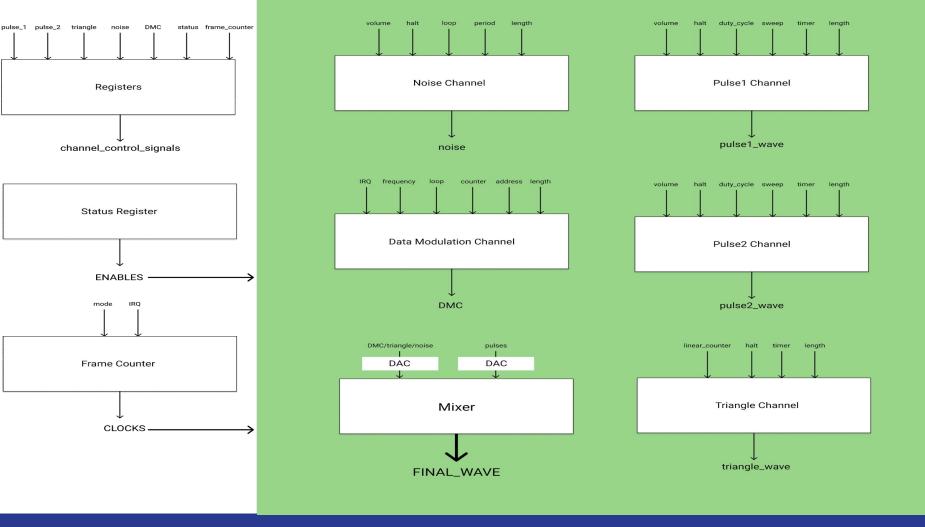

### System Specification - APU

- CPU specifies properties to APU's channels

- Frame counter provides clocks for channels

- The 5 major channels generate waves

- Noise creates pseudorandom noise

- DMC plays differential pulse code modulation samples

- Pulse 1 & 2 produces a pulse wave of varying duty cycle, period, etc

- Triangle produces a triangle wave of variable frequency

- Channel waves are converted to analog

- All waves are mixed for final audio output

## Metrics and validation

- Frame Accuracy

- emulator frame will be compared against ours to check for differences

- Cycle Accuracy

- PPU: Status signals from register trigger and can be read at correct cycle

- CPU: use a reference simulator to verify instructions run cycle accurate

- Memory Accuracy

- PPU: use emulator scripts to dump Nametable, OAM, Pattern table and compare against our memory trace

- CPU: use a reference simulator to verify memory traces are accurate.

### **Project Management**

| Week of | Nikolai | Diego | Oscar | Notable dates       | 0  | Slack                                 |    |                               |

|---------|---------|-------|-------|---------------------|----|---------------------------------------|----|-------------------------------|

| 02/11   | 1       | 12    | 12    |                     | 1  | Research CPU                          |    |                               |

| 02/14   | 1       | 34    | 34    |                     | 2  | Write Micro Code                      | 24 | Design Doc                    |

| 02/18   | 2       | 13    | 35    |                     | 3  | Implement C Simulator                 | 25 | Design Presentation           |

| 02/21   | 2       | 14    | 36    |                     | 4  | Implement SV Implementation           | 26 | Final Report                  |

| 02/25   | 3       | 15    | 37    |                     | 5  | Test CPU instructions                 | 27 | Final Presentation            |

| 02/28   | 24      | 24    | 24    |                     | 6  | Create controller interface           | 28 | Integration                   |

| 03/04   | 4       | 14    | 14    | Design Doc          | 7  | Test controller interface             | 29 |                               |

| 03/07   | 5       | 16    | 16    |                     | 8  | Serialize game state data             | 30 |                               |

| 03/11   | 0       | 0     | 0     | Spring break        | 9  | Deserialize game state data           | 31 |                               |

| 03/14   | 0       | 0     | 0     | Spring break        | 10 | Test serilization                     | 32 |                               |

| 03/18   | 28      | 28    | 28    |                     | 11 | Create flash memory controller        | 33 |                               |

| 03/21   | 28      | 28    | 28    |                     | 12 | PPU research                          | 34 | PPU Sprite Simulator          |

| 03/25   | 6       | 16    | 16    |                     | 13 | Generate Foreground sprites           | 35 | PPU Timing analysis           |

| 03/28   | 7       | 8     | 17    |                     | 14 | Generate Background sprites           | 36 | PPU Background rendering FPGA |

| 04/01   | 11      | 9     | 22    |                     | 15 | Create Frame by combining sprites     | 37 | PPU Sprite rendering FPGA     |

| 04/04   | 28      | 10    | 23    |                     | 16 | Test generated frames                 | 38 |                               |

| 04/08   | 28      | 18    | 28    |                     | 17 | VGA module                            | 39 |                               |

| 04/11   | 28      | 19    | 28    |                     | 18 | APU to CPU interface                  | 40 |                               |

| 04/15   | 28      | 20    | 28    |                     | 19 | APU to speaker mixing scheme          | 41 |                               |

| 04/18   | 0       | 28    | 0     |                     | 20 | Test APU                              | 42 |                               |

| 04/22   | 0       | 0     | 0     |                     | 21 | PWM module for speaker                | 43 |                               |

| 04/25   | 27      | 27    | 27    |                     | 22 | Load ROM into SRAM                    | 44 |                               |

| 04/29   | 26      | 26    | 26    | Final Presentations | 23 | Testing framework with Mesen emulator | 45 |                               |

| 05/02   | 26      | 26    | 26    | Demo                |    |                                       |    |                               |

| 05/06   |         |       |       | Final Report Due    |    |                                       |    |                               |