### 18-447

# Computer Architecture Lecture 4: ISA Tradeoffs (Continued) and Single-Cycle Microarchitectures

Prof. Onur Mutlu

Carnegie Mellon University

Spring 2014, 1/22/2014

# X86: Small Semantic Gap: String Operations

```

REP MOVS (DEST SRC)

DEST \leftarrow SRC:

IF (Byte move)

THEN IF DF = 0

THEN

(R|E)SI \leftarrow (R|E)SI + 1;

IF AddressSize = 16

(R|E)DI \leftarrow (R|E)DI + 1;

THEN

ELSE

(R|E)SI \leftarrow (R|E)SI - 1;

Use CX for CountReg;

(R|E)DI \leftarrow (R|E)DI - 1;

ELSE IF AddressSize = 64 and REX.W used

ELSE IF (Word move)

THEN Use RCX for CountReg; FI;

THEN IF DF = 0

(R|E)SI \leftarrow (R|E)SI + 2;

ELSE

(R|E)DI \leftarrow (R|E)DI + 2;

Use ECX for CountReg;

ELSE

FI:

(R|E)SI \leftarrow (R|E)SI - 2;

(R|E)DI \leftarrow (R|E)DI - 2;

WHILE CountReg \neq 0

D0

ELSE IF (Doubleword move)

THEN IF DF = 0

Service pending interrupts (if any);

(R|E)SI \leftarrow (R|E)SI + 4;

(R|E)DI \leftarrow (R|E)DI + 4;

Execute associated string instruction;

FI:

ELSE

CountReg \leftarrow (CountReg - 1);

(R|E)SI \leftarrow (R|E)SI - 4;

IF CountReq = 0

(R|E)DI \leftarrow (R|E)DI - 4;

THEN exit WHILE loop; FI;

ELSE IF (Quadword move)

IF (Repeat prefix is REPZ or REPE) and (ZF = 0)

THEN IF DF = 0

(R|E)SI \leftarrow (R|E)SI + 8;

or (Repeat prefix is REPNZ or REPNE) and (ZF = 1)

(R|E)DI \leftarrow (R|E)DI + 8;

FI:

THEN exit WHILE loop; FI;

ELSE

OD;

(R|E)SI \leftarrow (R|E)SI - 8;

(R|E)DI \leftarrow (R|E)DI - 8;

FI;

```

How many instructions does this take in ARM and MIPS?

# Small Semantic Gap Examples in VAX

- FIND FIRST

- Find the first set bit in a bit field

- Helps OS resource allocation operations

- SAVE CONTEXT, LOAD CONTEXT

- Special context switching instructions

- INSQUEUE, REMQUEUE

- Operations on doubly linked list

- INDEX

- Array access with bounds checking

- STRING Operations

- Compare strings, find substrings, ...

- Cyclic Redundancy Check Instruction

- EDITPC

- Implements editing functions to display fixed format output

- Digital Equipment Corp., "VAX11 780 Architecture Handbook," 1977-78.

# Small versus Large Semantic Gap

### CISC vs. RISC

- □ Complex instruction set computer → complex instructions

- Initially motivated by "not good enough" code generation

- □ Reduced instruction set computer → simple instructions

- John Cocke, mid 1970s, IBM 801

- Goal: enable better compiler control and optimization

### RISC motivated by

- Memory stalls (no work done in a complex instruction when there is a memory stall?)

- When is this correct?

- □ Simplifying the hardware → lower cost, higher frequency

- Enabling the compiler to optimize the code better

- Find fine-grained parallelism to reduce stalls

# How High or Low Can You Go?

### Very large semantic gap

- Each instruction specifies the complete set of control signals in the machine

- Compiler generates control signals

- Open microcode (John Cocke, circa 1970s)

- Gave way to optimizing compilers

### Very small semantic gap

- ISA is (almost) the same as high-level language

- Java machines, LISP machines, object-oriented machines, capability-based machines

### A Note on ISA Evolution

ISAs have evolved to reflect/satisfy the concerns of the day

### Examples:

- Limited on-chip and off-chip memory size

- Limited compiler optimization technology

- Limited memory bandwidth

- Need for specialization in important applications (e.g., MMX)

- Use of translation (in HW and SW) enabled underlying implementations to be similar, regardless of the ISA

- Concept of translation/interpretation interface

- Contrast it with hardware/software interface

### Effect of Translation

One can translate from one ISA to another ISA to change the semantic gap tradeoffs

### Examples

- Intel's and AMD's x86 implementations translate x86 instructions into programmer-invisible microoperations (simple instructions) in hardware

- Transmeta's x86 implementations translated x86 instructions into "secret" VLIW instructions in software (code morphing software)

- Think about the tradeoffs

# ISA-level Tradeoffs: Instruction Length

- Fixed length: Length of all instructions the same

- + Easier to decode single instruction in hardware

- + Easier to decode multiple instructions concurrently

- -- Wasted bits in instructions (Why is this bad?)

- -- Harder-to-extend ISA (how to add new instructions?)

- Variable length: Length of instructions different (determined by opcode and sub-opcode)

- + Compact encoding (Why is this good?)

Intel 432: Huffman encoding (sort of). 6 to 321 bit instructions. How?

- -- More logic to decode a single instruction

- -- Harder to decode multiple instructions concurrently

### Tradeoffs

- Code size (memory space, bandwidth, latency) vs. hardware complexity

- ISA extensibility and expressiveness vs. hardware complexity

- Performance? Smaller code vs. ease of decode

### ISA-level Tradeoffs: Uniform Decode

- Uniform decode: Same bits in each instruction correspond to the same meaning

- Opcode is always in the same location

- Ditto operand specifiers, immediate values, ...

- Many "RISC" ISAs: Alpha, MIPS, SPARC

- + Easier decode, simpler hardware

- + Enables parallelism: generate target address before knowing the instruction is a branch

- -- Restricts instruction format (fewer instructions?) or wastes space

### Non-uniform decode

- E.g., opcode can be the 1st-7th byte in x86

- + More compact and powerful instruction format

- -- More complex decode logic

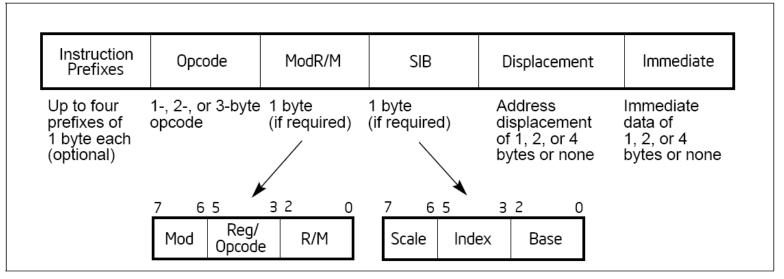

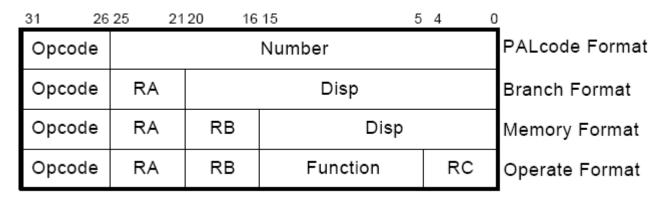

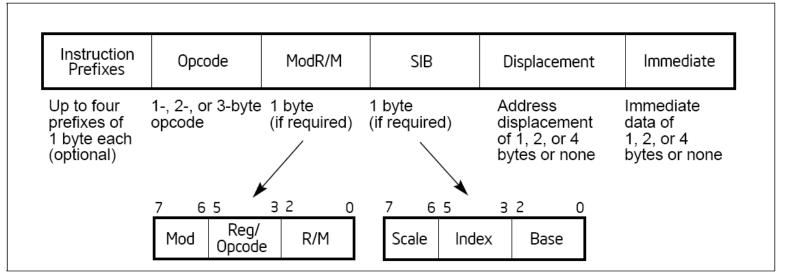

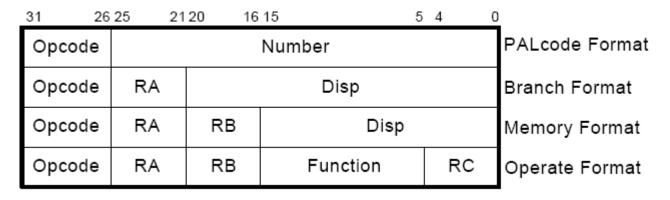

# x86 vs. Alpha Instruction Formats

### **x86**:

### Alpha:

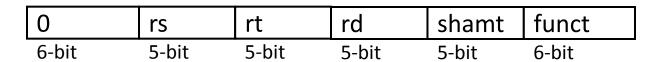

### MIPS Instruction Format

R-type, 3 register operands

I-type, 2 register operands and 16-bit immediate operand

| opcode | rs    | rt    | immediate | I-type |

|--------|-------|-------|-----------|--------|

| 6-hit  | 5-hit | 5-hit | 16-hit    | ·      |

J-type, 26-bit immediate operand

| opcode | immediate | J-type |

|--------|-----------|--------|

| 6-hit  | 26-hit    |        |

- Simple Decoding

- 4 bytes per instruction, regardless of format

- must be 4-byte aligned (2 lsb of PC must be 2b'00)

- format and fields easy to extract in hardware

R-type

####

| Cond | 0 | 0 | 1 | C | Opc | od                   | е                     | S |   | Rn  |   |    | R   | d   |     | Operand 2 |   |     |      |     |     |   |   |        |

|------|---|---|---|---|-----|----------------------|-----------------------|---|---|-----|---|----|-----|-----|-----|-----------|---|-----|------|-----|-----|---|---|--------|

| Cond | 0 | 0 | 0 | 0 | 0   | 0                    | Α                     | s |   | Rd  |   |    | R   | n   |     | Rs        |   |     |      | 1   | 0   | 0 | 1 | Rm     |

| Cond | 0 | 0 | 0 | 0 | 1   | U                    | Α                     | s | F | RdH | i | Г  | Rd  | Lo  |     |           | F | 'n  |      | 1   | 0   | 0 | 1 | Rm     |

| Cond | 0 | 0 | 0 | 1 | 0   | В                    | 0                     | 0 |   | Rn  |   | Γ  | R   | d   |     | 0         | 0 | 0   | 0    | 1   | 0   | 0 | 1 | Rm     |

| Cond | 0 | 0 | 0 | 1 | 0   | 0                    | 1                     | 0 | 1 | 1 1 | 1 | 1  | 1   | 1   | 1   | 1         | 1 | 1   | 1    | 0   | 0   | 0 | 1 | Rn     |

| Cond | 0 | 0 | 0 | Р | U   | 0                    | W                     | L |   | Rn  |   |    | R   | d   |     | 0         | 0 | 0   | 0    | 1   | S   | Н | 1 | Rm     |

| Cond | 0 | 0 | 0 | Р | U   | 1                    | w                     | L |   | Rn  |   |    | R   | d   |     | Offset    |   |     | et   | 1   | s   | Н | 1 | Offset |

| Cond | 0 | 1 | ı | Р | U   | В                    | w                     | L |   | Rn  |   | Н  | R   | d   |     | Offse     |   |     |      | set | et  |   |   |        |

| Cond | 0 | 1 | 1 |   |     |                      |                       |   |   |     |   |    |     |     |     |           |   |     |      |     |     |   | 1 |        |

| Cond | 1 | 0 | 0 | Р | U   | s                    | w                     | L |   | Rn  |   | Γ  |     |     |     |           | F | Reg | gist | er  | Lis | t | _ |        |

| Cond | 1 | 0 | 1 | L |     | _                    |                       |   |   |     |   | _  |     | (   | Off | set       | t |     |      |     |     |   |   |        |

| Cond | 1 | 1 | 0 | Р | U   | N                    | W L Rn CRd CP# Offset |   |   |     |   |    |     | set |     |           |   |     |      |     |     |   |   |        |

| Cond | 1 | 1 | 1 | 0 | (   | P                    | Ор                    | С | ( | CRn |   |    | CRd |     | CP# |           |   | CF  | )    | 0   | CRm |   |   |        |

| Cond | 1 | 1 | 1 | 0 | CI  | 0                    | рс                    | L | ( | CRn |   | Rd |     |     | CP# |           |   | CF  | )    | 1   | CRm |   |   |        |

| Cond | 1 | 1 | 1 | 1 |     | Ignored by processor |                       |   |   |     |   |    |     |     |     |           |   |     |      |     |     |   |   |        |

1 0

Data Processing / PSR Transfer

Multiply

Multiply Long

Single Data Swap

Branch and Exchange

Halfword Data Transfer: register offset

Halfword Data Transfer: immediate offset

Single Data Transfer

Undefined

Block Data Transfer

Branch

Coprocessor Data Transfer

Coprocessor Data Operation

Coprocessor Register Transfer

Software Interrupt

# A Note on Length and Uniformity

- Uniform decode usually goes with fixed length

- In a variable length ISA, uniform decode can be a property of instructions of the same length

- It is hard to think of it as a property of instructions of different lengths

### A Note on RISC vs. CISC

Usually, ...

### RISC

- Simple instructions

- Fixed length

- Uniform decode

- Few addressing modes

### CISC

- Complex instructions

- Variable length

- Non-uniform decode

- Many addressing modes

# ISA-level Tradeoffs: Number of Registers

### Affects:

- Number of bits used for encoding register address

- Number of values kept in fast storage (register file)

- (uarch) Size, access time, power consumption of register file

### Large number of registers:

- + Enables better register allocation (and optimizations) by compiler → fewer saves/restores

- -- Larger instruction size

- -- Larger register file size

# ISA-level Tradeoffs: Addressing Modes

- Addressing mode specifies how to obtain an operand of an instruction

- Register

- Immediate

- Memory (displacement, register indirect, indexed, absolute, memory indirect, autoincrement, autodecrement, ...)

### More modes:

- + help better support programming constructs (arrays, pointerbased accesses)

- -- make it harder for the architect to design

- -- too many choices for the compiler?

- Many ways to do the same thing complicates compiler design

- Wulf, "Compilers and Computer Architecture," IEEE Computer 1981

# x86 vs. Alpha Instruction Formats

### **x86**:

### Alpha:

|          | Table 2-2                                                                                                                                                                   | . 32-6 | Bit Add                                              | ressin                                       | g Form                                       | s with                                       | the M                                        | odR/M                                        | l Byte                                                                                       |                                              |                                                                                              |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

|          | r8(/r)<br>r16(/r)<br>r32(/r)<br>mm(/r)<br>xmm(/r)<br>(In decimal) /digit (Opcode)<br>(In binary) REG =                                                                      |        |                                                      | AL<br>AX<br>EAX<br>MMO<br>XMMO<br>0<br>0     | CL<br>CX<br>ECX<br>MM1<br>XMM1<br>1<br>001   | DL<br>DX<br>EDX<br>MM2<br>XMM2<br>2<br>010   | BL<br>BX<br>EBX<br>MM3<br>XMM3<br>3<br>011   | AH<br>SP<br>ESP<br>MM4<br>XMM4<br>4<br>100   | CH<br>BP<br>EBP<br>MM5<br>XMM5<br>5<br>101                                                   | DH<br>SI<br>ESI<br>MM6<br>XMM6<br>6<br>110   | BH<br>DI<br>EDI<br>MM7<br>XMM7<br>7<br>111                                                   |  |  |

|          | Effective Address                                                                                                                                                           | Mod    | R/M                                                  | Value of ModR/M Byte (in Hexadecimal)        |                                              |                                              |                                              |                                              |                                                                                              |                                              |                                                                                              |  |  |

| <u></u>  | [EAX]<br>(EDX)<br>(EBX)<br>(-)[-] <sup>1</sup><br>disp32 <sup>2</sup><br>(ESI)<br>(EDI)                                                                                     | 00     | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07 | 08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F | 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | 18<br>19<br>1A<br>1B<br>1C<br>1D<br>1E<br>1F | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | 28<br>29<br>2A<br>2B<br>2C<br>2D<br>2E<br>2F                                                 | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 389<br>380<br>380<br>380<br>380<br>380<br>380<br>380<br>380<br>380<br>380                    |  |  |

| <u> </u> | [EAX]+disp8 <sup>3</sup> [ECX]+disp8 [EDX]+disp8 [EBX]+disp8 [][]+disp8 [ESI]+disp8 [EDI]+disp8                                                                             | 01     | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47 | 48<br>49<br>4A<br>4B<br>4C<br>4D<br>4E<br>4F | 50<br>551<br>552<br>554<br>555<br>557        | 58<br>59<br>5A<br>5B<br>5C<br>5D<br>5E<br>5F | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | 68<br>69<br>6A<br>6B<br>6C<br>6D<br>6E<br>6F                                                 | 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77 | 78<br>79<br>7A<br>7B<br>7C<br>7D<br>7E<br>7F                                                 |  |  |

|          | [EAX]+disp32<br>[ECX]+disp32<br>[EDX]+disp32<br>[EBX]+disp32<br>[](]+disp32<br>[EBP]+disp32<br>[ESI]+disp32<br>[EDI]+disp32                                                 | 10     | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 80<br>81<br>82<br>83<br>84<br>85<br>86<br>87 | 88<br>89<br>8A<br>8B<br>8C<br>8D<br>8E<br>8F | 90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | 98<br>99<br>9A<br>9B<br>9C<br>9D<br>9E<br>9F | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7 | A8<br>A9<br>AA<br>AB<br>AC<br>AD<br>AE<br>AF                                                 | B0<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7 | 88<br>89<br>8A<br>8B<br>8B<br>8D<br>8E<br>8F                                                 |  |  |

|          | EAX/AX/AL/MM0/XMM0<br>ECX/CX/CL/MM/XMM1<br>EDX/DX/DL/MM2/XMM2<br>EBX/BX/BL/MM3/XMM3<br>ESP/SP/AH/MM4/XMM4<br>EBP/BP/CH/MM5/XMM5<br>ESI/SI/DH/MM6/XMM6<br>EDI/DI/BH/MM7/XMM7 | 11     | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 85884565                                     | 8<br>9<br>CA<br>BC<br>CB<br>CC<br>CE<br>CF   | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | D8<br>D9<br>DA<br>DB<br>DC<br>DD<br>DE<br>DF | 81284567                                     | 89<br>69<br>68<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60 | F0<br>F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7 | 89<br>68<br>68<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60 |  |  |

#### NOTES:

x86

register

indirect

absolute

register +

displacement

register

- The [--][--] nomenclature means a SIB follows the ModR/M byte.

- 2. The disp32 nomenclature denotes a 32-bit displacement that follows the ModR/M byte (or the SIB byte if one is present) and that is added to the index.

- 3. The disp8 nomenclature denotes an 8-bit displacement that follows the ModR/M byte (or the SIB byte if one is present) and that is sign-extended and added to the index.

Table 2-3 is organized to give 256 possible values of the SIB byte (in hexadecimal). General numbose registers used as a base are indicated across the top of the table.

x86

indexed

(base +

index)

scaled

(base +

index\*4)

Table 2-3. 32-Bit Addressing Forms with the SIB Byte

|   |                                                                                   | Table 2 | -3. 32                                               | -BIT Ad                                      | dressin                                      | g Form                                       | s with :                                           | tue 21R                                      | Byte                                         |                                                    |                                              |  |  |  |  |

|---|-----------------------------------------------------------------------------------|---------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------|--|--|--|--|

|   | r32<br>(In decimal) Base =<br>(In binary) Base =                                  |         |                                                      | EAX<br>0<br>000                              | ECX<br>1<br>001                              | EDX<br>2<br>010                              | EBX<br>3<br>011                                    | ESP<br>4<br>100                              | [*]<br>5<br>101                              | ESI<br>6<br>110                                    | EDI<br>7<br>111                              |  |  |  |  |

| - | Scaled Index                                                                      | SS      | Index                                                | Value of SIB Byte (in Hexadecimal)           |                                              |                                              |                                                    |                                              |                                              |                                                    |                                              |  |  |  |  |

|   | [EAX]<br>[ECX]<br>[EDX]<br>[EBX]<br>none<br>[EBP]<br>[ESI]<br>[EDI]               | 00      | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>08<br>10<br>18<br>20<br>28<br>38       | 01<br>09<br>11<br>19<br>21<br>29<br>31<br>39 | 02<br>0A<br>12<br>1A<br>22<br>2A<br>33A      | 03<br>0B<br>13<br>1B<br>23<br>2B<br>33B            | 04<br>00<br>14<br>10<br>24<br>20<br>34<br>30 | 05<br>0D<br>15<br>1D<br>25<br>2D<br>35<br>3D | 06<br>0E<br>1E<br>1E<br>2E<br>3E                   | 07<br>0F<br>17<br>1F<br>27<br>2F<br>37<br>3F |  |  |  |  |

|   | [EAX*2]<br>[ECX*2]<br>[EDX*2]<br>[EBX*2]<br>none<br>[EBP*2]<br>[ESI*2]<br>[EDI*2] | 01      | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 40<br>48<br>50<br>58<br>60<br>68<br>70<br>78 | 41<br>49<br>51<br>59<br>61<br>69<br>71<br>79 | 42<br>4A<br>52<br>5A<br>62<br>6A<br>72<br>7A | 43<br>4B<br>53<br>5B<br>63<br>6B<br>73<br>7B       | 44<br>40<br>54<br>50<br>64<br>60<br>74<br>70 | 45<br>4D<br>55<br>5D<br>65<br>6D<br>75<br>7D | 46<br>4E<br>56<br>5E<br>66<br>6E<br>7E             | 47<br>4F<br>57<br>5F<br>67<br>6F<br>77<br>7F |  |  |  |  |

| 7 | [EAX*4]<br>[ECX*4]<br>[EDX*4]<br>[EBX*4]<br>none<br>[EBP*4]<br>[ESI*4]<br>[EDI*4] | 10      | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 80<br>88<br>90<br>98<br>A0<br>A8<br>B0<br>B8 | 81<br>89<br>91<br>89<br>A1<br>A9<br>B1<br>B9 | 82<br>8A<br>92<br>9A<br>A2<br>AA<br>B2<br>BA | 83<br>88<br>93<br>98<br>83<br>88<br>88<br>88<br>88 | 84<br>8C<br>94<br>9C<br>A4<br>AC<br>B4<br>BC | 85<br>8D<br>95<br>9D<br>A5<br>AD<br>B5<br>BD | 86<br>86<br>96<br>96<br>86<br>86<br>86<br>86<br>86 | 87<br>8F<br>97<br>9F<br>A7<br>AF<br>B7<br>BF |  |  |  |  |

|   | [EAX*8]<br>ECX*8]<br>EDX*8]<br>EBX*8]<br>none<br>[EBP*8]<br>[ESI*8]<br>[EDI*8]    | 11      | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | C&688886                                     | C1<br>C9<br>D9<br>E1<br>E9<br>F1<br>F9       | CACACACACACACACACACACACACACACACACACACA       | 083808CE                                           | 46464646                                     | 56565656                                     | 666666666                                          | C7<br>CF<br>D7<br>DF<br>E7<br>EF<br>F7<br>FF |  |  |  |  |

#### NOTES:

#### MOD bits Effective Address

- 00 [scaled index] + disp32

- 01 [scaled index] + disp8 + [EBP]

- 10 [scaled index] + disp32 + [EBP]

The [\*] nomenclature means a disp32 with no base if the MOD is 00B. Otherwise, [\*] means disp8

or disp32 + [EBP]. This provides the following address modes:

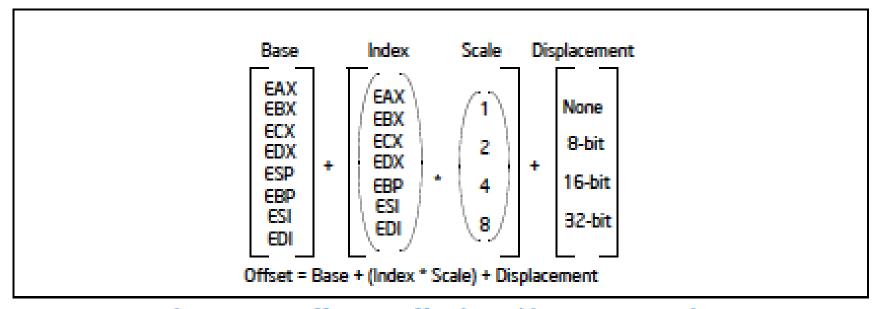

# X86 SIB-D Addressing Mode

Figure 3-11. Offset (or Effective Address) Computation

x86 Manual Vol. 1, page 3-22 -- see course resources on website Also, see Section 3.7.3 and 3.7.5

## X86 Manual: Suggested Uses of Addressing Modes

The following addressing modes suggest uses for common combinations of address components.

- Displacement A displacement alone represents a direct (uncomputed) offset to the operand. Because the

displacement is encoded in the instruction, this form of an address is sometimes called an absolute or static

address. It is commonly used to access a statically allocated scalar operand.

- Base A base alone represents an indirect offset to the operand. Since the value in the base register can

change, it can be used for dynamic storage of variables and data structures.

- Base + Displacement A base register and a displacement can be used together for two distinct purposes:

- As an index into an array when the element size is not 2, 4, or 8 bytes—The displacement component

encodes the static offset to the beginning of the array. The base register holds the results of a calculation to

determine the offset to a specific element within the array.

- To access a field of a record: the base register holds the address of the beginning of the record, while the

displacement is a static offset to the field.

An important special case of this combination is access to parameters in a procedure activation record. A procedure activation record is the stack frame created when a procedure is entered. Here, the EBP register is the best choice for the base register, because it automatically selects the stack segment. This is a compact encoding for this common function.

x86 Manual Vol. 1, page 3-22 -- see course resources on website Also, see Section 3.7.3 and 3.7.5

# X86 Manual: Suggested Uses of Addressing Modes

- (Index \* Scale) + Displacement This address mode offers an efficient way

to index into a static array when the element size is 2, 4, or 8 bytes. The

displacement locates the beginning of the array, the index register holds the

subscript of the desired array element, and the processor automatically converts

the subscript into an index by applying the scaling factor.

- Base + Index + Displacement Using two registers together supports either

a two-dimensional array (the displacement holds the address of the beginning of

the array) or one of several instances of an array of records (the displacement is

an offset to a field within the record).

- Base + (Index \* Scale) + Displacement Using all the addressing components together allows efficient indexing of a two-dimensional array when the elements of the array are 2, 4, or 8 bytes in size.

x86 Manual Vol. 1, page 3-22 -- see course resources on website Also, see Section 3.7.3 and 3.7.5

# Other Example ISA-level Tradeoffs

- Condition codes vs. not

- VLIW vs. single instruction

- Precise vs. imprecise exceptions

- Virtual memory vs. not

- Unaligned access vs. not

- Hardware interlocks vs. software-guaranteed interlocking

- Software vs. hardware managed page fault handling

- Cache coherence (hardware vs. software)

- **...**

# Back to Programmer vs. (Micro)architect

- Many ISA features designed to aid programmers

- But, complicate the hardware designer's job

- Virtual memory

- vs. overlay programming

- Should the programmer be concerned about the size of code blocks fitting physical memory?

- Addressing modes

- Unaligned memory access

- Compile/programmer needs to align data

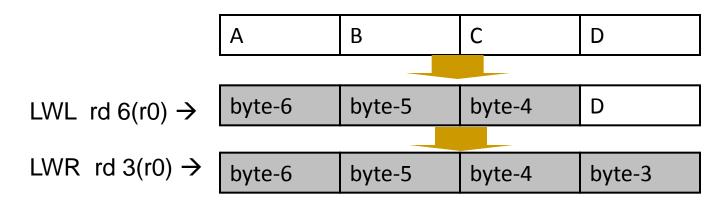

# MIPS: Aligned Access

| MSB | byte-3 | byte-2 | byte-1 | byte-0 | LSB |

|-----|--------|--------|--------|--------|-----|

|     | byte-7 | byte-6 | byte-5 | byte-4 |     |

- LW/SW alignment restriction: 4-byte word-alignment

- not designed to fetch memory bytes not within a word boundary

- not designed to rotate unaligned bytes into registers

- Provide separate opcodes for the "infrequent" case

- LWL/LWR is slower

- Note LWL and LWR still fetch within word boundary

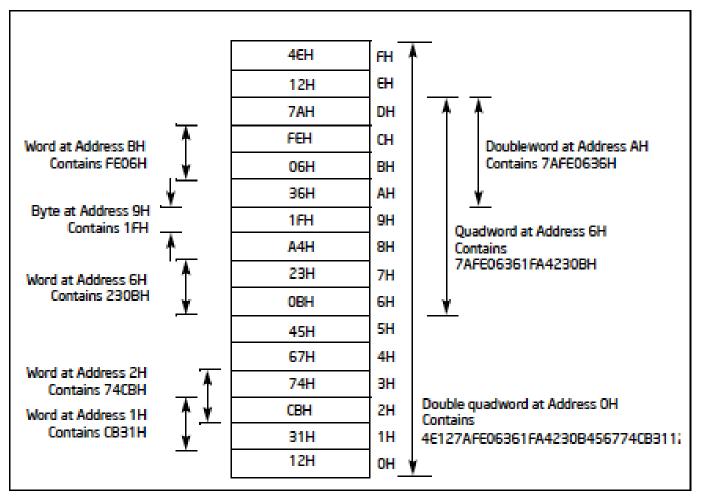

# X86: Unaligned Access

- LD/ST instructions automatically align data that spans a "word" boundary

- Programmer/compiler does not need to worry about where data is stored (whether or not in a word-aligned location)

### 4.1.1 Alignment of Words, Doublewords, Quadwords, and Double Quadwords

Words, doublewords, and quadwords do not need to be aligned in memory on natural boundaries. The natural boundaries for words, double words, and quadwords are even-numbered addresses, addresses evenly divisible by four, and addresses evenly divisible by eight, respectively. However, to improve the performance of programs, data structures (especially stacks) should be aligned on natural boundaries when ever possible. The reason for this is that the processor requires two memory accesses to make an unaligned memory access; aligned accesses require only one memory access. A word or doubleword operand that crosses a 4-byte boundary or a quadword operand that crosses an 8-byte boundary is considered unaligned and requires two separate memory bus cycles for access.

# X86: Unaligned Access

Figure 4-2. Bytes, Words, Doublewords, Quadwords, and Double Quadwords in Memory

### What About ARM?

- https://www.scss.tcd.ie/~waldroj/3d1/arm\_arm.pdf

- Section A2.8

# Aligned vs. Unaligned Access

Pros of having no restrictions on alignment

Cons of having no restrictions on alignment

Filling in the above: an exercise for you...

# Implementing the ISA: Microarchitecture Basics

### How Does a Machine Process Instructions?

- What does processing an instruction mean?

- Remember the von Neumann model

A = Architectural (programmer visible) state before an instruction is processed

Process instruction

A' = Architectural (programmer visible) state after an instruction is processed

Processing an instruction: Transforming A to A' according to the ISA specification of the instruction

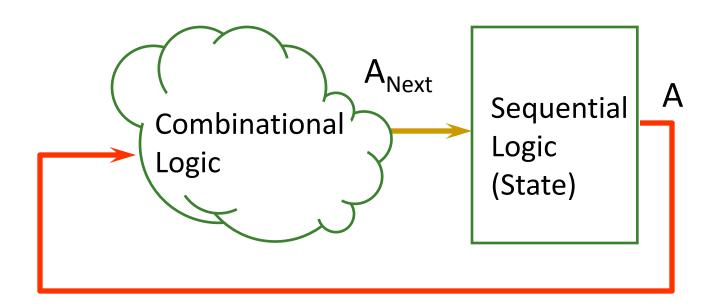

# The "Process instruction" Step

- ISA specifies abstractly what A' should be, given an instruction and A

- It defines an abstract finite state machine where

- State = programmer-visible state

- Next-state logic = instruction execution specification

- From ISA point of view, there are no "intermediate states" between A and A' during instruction execution

- One state transition per instruction

- Microarchitecture implements how A is transformed to A'

- There are many choices in implementation

- We can have programmer-invisible state to optimize the speed of instruction execution: multiple state transitions per instruction

- Choice 1:  $A \rightarrow A'$  (transform A to A' in a single clock cycle)

- Choice 2: A → A+MS1 → A+MS2 → A+MS3 → A' (take multiple clock cycles to transform A to A')

# A Very Basic Instruction Processing Engine

- Each instruction takes a single clock cycle to execute

- Only combinational logic is used to implement instruction execution

- No intermediate, programmer-invisible state updates

A = Architectural (programmer visible) state at the beginning of a clock cycle

Process instruction in one clock cycle

A' = Architectural (programmer visible) state at the end of a clock cycle

# A Very Basic Instruction Processing Engine

Single-cycle machine

- What is the clock cycle time determined by?

- What is the *critical path* of the combinational logic determined by?

## Remember: Programmer Visible (Architectural) State

| M[0]   |

|--------|

| M[1]   |

| M[2]   |

| M[3]   |

| M[4]   |

|        |

|        |

|        |

|        |

| M[N-1] |

#### Registers

- given special names in the ISA (as opposed to addresses)

- general vs. special purpose

#### Memory

array of storage locations indexed by an address

#### **Program Counter**

memory address

of the current instruction

Instructions (and programs) specify how to transform the values of programmer visible state

# Single-cycle vs. Multi-cycle Machines

### Single-cycle machines

- Each instruction takes a single clock cycle

- All state updates made at the end of an instruction's execution

- Big disadvantage: The slowest instruction determines cycle time → long clock cycle time

### Multi-cycle machines

- Instruction processing broken into multiple cycles/stages

- State updates can be made during an instruction's execution

- Architectural state updates made only at the end of an instruction's execution

- Advantage over single-cycle: The slowest "stage" determines cycle time

- Both single-cycle and multi-cycle machines literally follow the von Neumann model at the microarchitecture level

# Instruction Processing "Cycle"

- Instructions are processed under the direction of a "control unit" step by step.

- Instruction cycle: Sequence of steps to process an instruction

- Fundamentally, there are six phases:

- Fetch

- Decode

- Evaluate Address

- Fetch Operands

- Execute

- Store Result

- Not all instructions require all six stages (see P&P Ch. 4)

### Instruction Processing "Cycle" vs. Machine Clock Cycle

- Single-cycle machine:

- All six phases of the instruction processing cycle take a single machine clock cycle to complete

- Multi-cycle machine:

- All six phases of the instruction processing cycle can take multiple machine clock cycles to complete

- In fact, each phase can take multiple clock cycles to complete

# Instruction Processing Viewed Another Way

- Instructions transform Data (AS) to Data' (AS')

- This transformation is done by functional units

- Units that "operate" on data

- These units need to be told what to do to the data

- An instruction processing engine consists of two components

- Datapath: Consists of hardware elements that deal with and transform data signals

- functional units that operate on data

- hardware structures (e.g. wires and muxes) that enable the flow of data into the functional units and registers

- storage units that store data (e.g., registers)

- Control logic: Consists of hardware elements that determine control signals, i.e., signals that specify what the datapath elements should do to the data

# Single-cycle vs. Multi-cycle: Control & Data

- Single-cycle machine:

- Control signals are generated in the same clock cycle as data signals are operated on

- Everything related to an instruction happens in one clock cycle

- Multi-cycle machine:

- Control signals needed in the next cycle can be generated in the previous cycle

- Latency of control processing can be overlapped with latency of datapath operation

- We will see the difference clearly in microprogrammed multi-cycle microarchitecture

# Many Ways of Datapath and Control Design

- There are many ways of designing the data path and control logic

- Single-cycle, multi-cycle, pipelined datapath and control

- Single-bus vs. multi-bus datapaths

- See your homework 2 question

- Hardwired/combinational vs. microcoded/microprogrammed control

- Control signals generated by combinational logic versus

- Control signals stored in a memory structure

- Control signals and structure depend on the datapath design

# Flash-Forward: Performance Analysis

- Execution time of an instruction

- CPI x {clock cycle time}

- Execution time of a program

- Sum over all instructions [{CPI} x {clock cycle time}]

- {# of instructions} x {Average CPI} x {clock cycle time}

- Single cycle microarchitecture performance

- $\Box$  CPI = 1

- Clock cycle time = long

- Multi-cycle microarchitecture performance

- CPI = different for each instruction

- Average CPI → hopefully small

- □ Clock cycle time = short

Now, we have two degrees of freedom to optimize independently