# (Lec 10) Technology Mapping

- What you know: Synthesis--all there is

- ▶ 2-level ESPRESSO style

- ► Multi-level style

- > Structural modifications to Boolean Logic Network

- > Subexpression extraction: cube & kernel extraction

- > Vertex simplification via multi-level don't cares

- ▶ Clever representation schemes to make these doable

- **▷ PCN inside ESPRESSO**

- **BDDs** everywhere else

- **■** What you don't know

- ► How a synthesized multi-level logic network gets turned into real, live, usable gates in your implementation

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 1

# **Copyright Notice**

© Rob A. Rutenbar 2001 All rights reserved.

You may not make copies of this material in any form without my express permission.

© R. Rutenbar 2001,

# Where Are We?

■ After logic synthesis--how to map to real library of gates?

|          | M  | Т  | W   | Th | F  |       |

|----------|----|----|-----|----|----|-------|

| Aug      | 27 | 28 | 29  | 30 | 31 | 1     |

| Sep      | 3  | 4  | 5   | 6  | 7  | 2     |

|          | 10 | П  | 12  | 13 | 14 | 3     |

|          | 17 | 18 | 19  | 20 | 21 | 4     |

|          | 24 | 25 | 26  | 27 | 28 | 5     |

| Oct      |    | 2  | 3   | 4  | 5  | 6     |

|          | 8  | 9  | 10  | П  | 12 | 7     |

| Midsem   | 15 | 16 | 17  | 18 | 19 | 8     |

| break 🌂  | 22 | 23 | 24  | 25 | 26 | 9     |

|          | 29 | 30 | 3 I | 1  | 2  | 10    |

| Nov      | 5  | 6  | 7   | 8  | 9  | $\Pi$ |

|          | 12 | 13 | 14  | 15 | 16 | 12    |

| Thnxgive | 19 | 20 | 21  | 22 | 23 | 13    |

|          | 26 | 27 | 28  | 29 | 30 | 14    |

| Dec      | 3  | 4  | 5   | 6  | 7  | 15    |

|          | 10 | П  | 12  | 13 | 14 | 16    |

|          |    |    |     |    |    |       |

Introduction

Advanced Boolean algebra

JAVA Review

Formal verification

2-Level logic synthesis

Multi-level logic synthesis

Technology mapping

Placement

Routing Static timing analysis Electrical timing analysis Geometric data structs & apps

© R. Rutenbar 2001, CMU 18-760, Fall 2001 3

# Readings

### **▼** De Micheli

- ► Chapter 10 is all about is all about technology mapping, which he calls "cell library binding"

- ▶ Read 10.1, 10.2, 10.3 (but only 10.3.1 here) and also 10.6

© R. Rutenbar 2001,

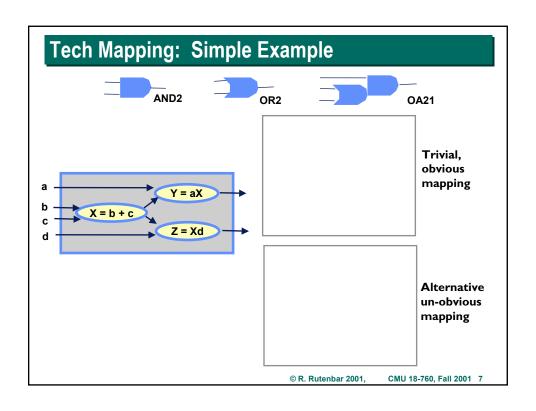

# **Tech Mapping: The Problem**

- Multi-level model is still a little abstract

- ▶ Structure of the Boolean logic network is fixed

- ▶ ESPRESSO-style 2-level simplification done on each node of network...

- ▶ But that still doesn't say what the actual gate-level netlist should be

- **▼**Trivial example

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 5

# **Tech Mapping: Problem**

- **▼** Suppose we have these gates in our "library"

- ▶ This is referred to as the "technology" we are allowed to use to actually build this optimized network

▶ OA21 is in OR-AND, a so-called complex gate in our library

How do we build the 2 functions specified in our Boolean Logic Network using ONLY these gates from our library?

© R. Rutenbar 2001,

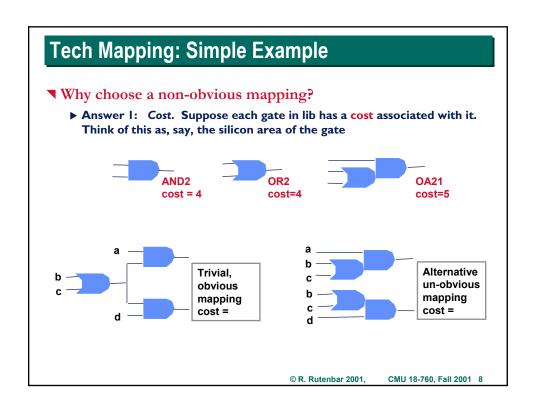

# **Tech Mapping**

- **▼** Why choose a non-obvious mapping?

- ▶ Answer 2: obvious parts not in your library

- ▶ Example: your library is only NOR and OR-AND-INVERT gates

- Even if you wanted to think about mapping your network into nice, vanilla ANDS and ORs and NOTs, you can't, because they are not in your library.

- ▶ Examples: in some Gallium Arsenide (GaAs) IC technologies, you only get NOR gates, period. In some dynamic CMOS logic styles, NORs are also the only thing you can do easily.

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 9

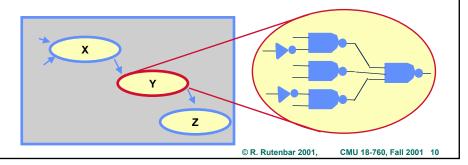

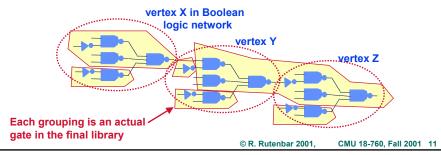

## **Tech Mapping: What Multilevel Synthesis Does**

- Helpful model to use: Multi-level synthesis does this...

- ▶ Structures the multiple-vertex Boolean logic network "well"

- ▶ Minimizes guts of each vertex in the network "well", ie, min literals

- ▶ But this is not real logic gates. This is "uncommitted" logic, or "technology independent" logic

- ▶ Think of it like this: it's only NANDs and NOTs, nothing else

# What "Technology Mapping" Does

#### **▼** Model

- ▶ So, synthesis gives you a network with the right overall structure...

- ▶ ...but not in terms of the gates you actually have to implement it with

### **▼** Tech mapping

- ▶ "Maps" output of synthesis, in "technology independent" form, into your actual gate library (Also called "binding" to the technology library)

- ▶ Important point: tech mapper is no longer required to respect the boundaries of vertices in the original Boolean logic network

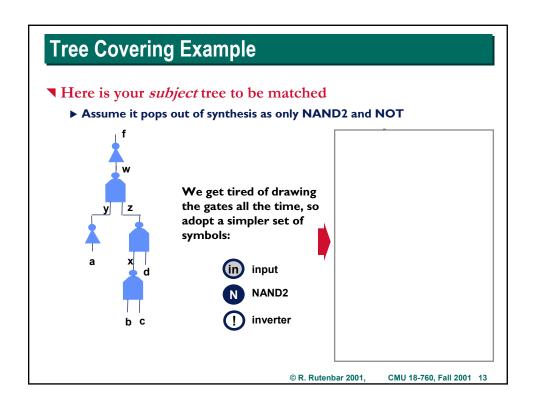

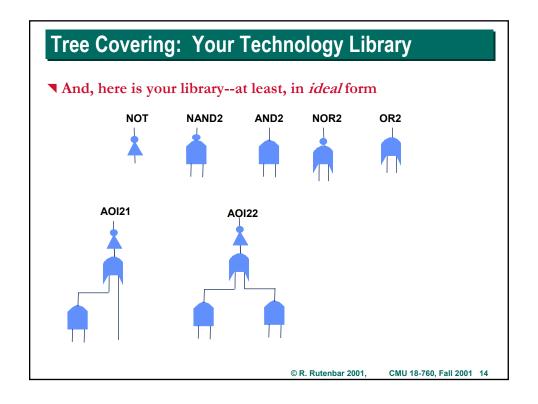

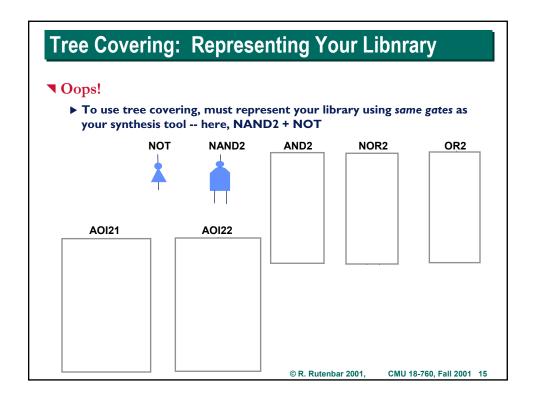

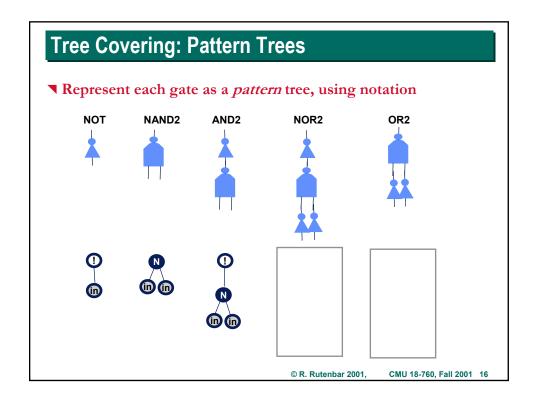

## **Technology Mapping as Tree Covering**

### **▼** One particularly useful, simple model of problem

- ▶ Your logic network to be mapped is a tree of simple gates

- > Easiest to assume absolutely minimal gate types

- ▷ Example: tech-independent form is 2 input NAND and NOT

- ▶ Your library of actual gate types is also available in this form

#### **▼** Problem

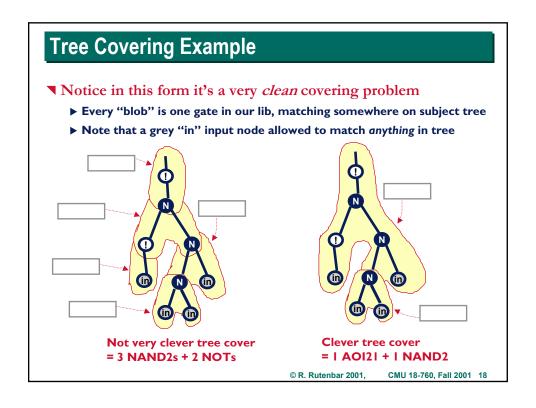

- "Cover" the tree that represents your tech-independent logiccalled the subject tree...

- ...with minimum cost set of gates (each a pattern tree) from lib

- ▶ Reduces tech mapping to: matching problem + a minimization problem

© R. Rutenbar 2001, CMU 18-760, Fall 2001 12

# **TechMap via Tree Covering**

- **▼** What do we need?

- **▼** Tree-ifying the input netlist

- ▶ Few assumptions need mentioning

- **▼**Tree matching

- ► For every node in your subject tree, need to know all the target pattern trees in your library that can match here

- Minimum cost covering

- ► Given you know what can match at each node of subject tree, which ones do you pick for a minimum cost cover?

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 19

# **Tree-ifying the Netlist**

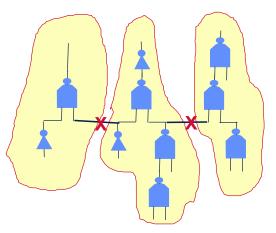

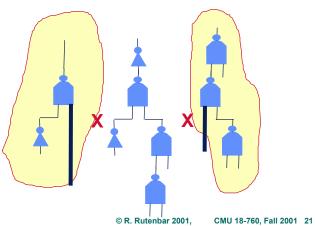

■ These algorithms only work on *trees*, not DAGs

Must split this DAG with fanouts into 3 separate trees, map each separately This entails some clear loss of optimality, since cannot map across trees

© R. Rutenbar 2001,

# **Tree-ifying Netlist**

- **▼** Our algorithms mandate trees, not DAGs

- ▶ Every place there is fanout from gate output > I, you have to cut

- **▶** Clearly loses some optimizations

- ▶ There are ways around this, but we won't look at them here...

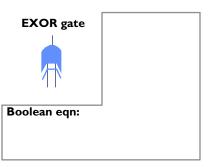

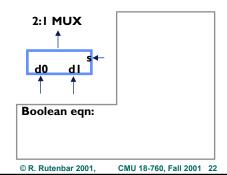

# Aside: How Restrictive is "Tree" Assumption?

- Subject graph and each pattern graph must be *trees*

- **■** Subject tree: must *tree-ify* it

- **▼** What about *pattern* trees?

- ▶ Are there any well-behaved 'gates' you would like in lib, but != trees?

- ▶ Unfortunately, yeah...

## **Tree Matching**

### **▼** There are several approaches

- ▶ Elegant, complicated approach: FSM matching

- > Treat subject tree like a special "string" of characters

- > Turn the pattern library into a Finite State Machine (FSM)

- ▷ Run the subject "string" thru the FSM, it tells you each place in subject tree that ANY tree in library matches

- > Fast, cool, hard to describe quickly (see book)

- ▶ Straightforward, not-so-fast, easy approach: Recursive matching

- ▷ Inputs: subject tree (root), a specific target pattern tree (root)

- Dutputs: each node in subject tree marked if pattern matches

- ▶ Note: need to run this algorithm for every target tree in library

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 23

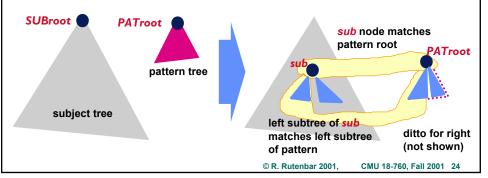

## **Recursive Tree Matching**

#### **▼** Ideas

- ▶ Start with subject tree root SUBroot, pattern tree root PATroot

- ▶ Do a tree walk on subject tree, visit every node--sub--of subject tree

- ▶ At each node of sub in walk, you call MATCH( sub, PATroot)

- ▶ The pattern tree matches here at sub if

- > sub node type same as PATroot node type, AND

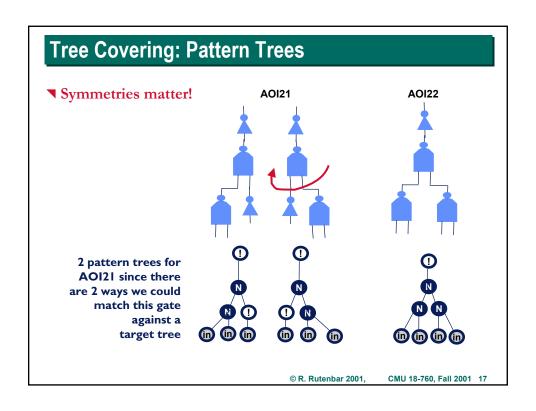

- ...each child of sub node recursively matches approp. child of PATroot

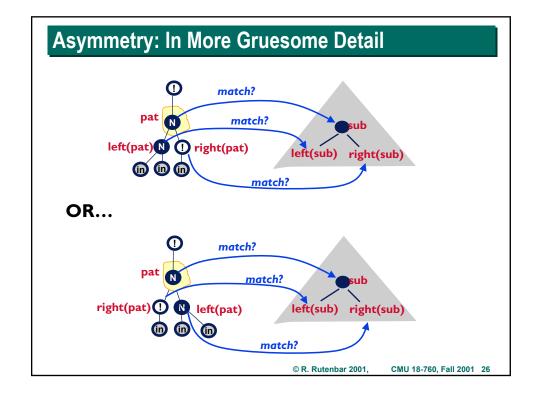

### **Tree Matching** ■ Well, it's slightly messier than that ▶ Inverters have only one child ▶ Node types > NAND matches NAND **▷ NOT** matches **NOT** > INPUT matches anything ▶ To handle asymmetric targets, must try BOTH these child matchings: > match (left(sub), right (pat)) && match (right(sub), left (pat)) match? AOI21 has 2 patterns, can deal with this pat just by cross-matching left(sub) right(sub) as shown above © R. Rutenbar 2001, CMU 18-760, Fall 2001 25

# **Tree Matching**

### **▼** Algorithm outline

```

MATCH( sub, pat) {

if ( nodetype( pat ) == INPUT )

then return (true); // input matches anything

if ( sub is a leaf of subject graph)

then return (false); // cannot be a match

if ( nodetype(pat) != nodetype(sub) )

then return (false); // cannot be a match

if ( nodetype(pat) == NOT ) { // only I child to recurse on

then return( MATCH( child(sub), child(pat) );

// it must be NAND2, so 2 children to recurse on

// just do the case where we assume pattern is asymmetric

return( MATCH( left(sub), left(pat)) && MATCH(right(sub), right(pat))

|| MATCH( left(sub), right(pat)) && MATCH(right(sub), left(pat)) );

}

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 27

```

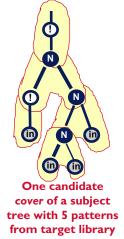

## **Minimum Cost Tree Covering**

#### **▼** Where are we?

- ▶ We tree-ified subject tree

- ▶ For each pattern tree in our library...

- ...we walked the nodes of the subject tree, root to leaves, recursively

- ...and at each node visited, we asked: MATCH(sub node, pat node)?

- ► Result: each node of subject now labeled with which pattern trees match it

### **Next problem:**

➤ What is the best cover of the subject tree with patterns from target lib?

© R. Rutenbar 2001,

# **Minimum Cost Covering of Subject Tree**

### **▼** Key insight

- ▶ If pattern P is min cost match at some node of subject tree...

- ► ...then it must be that each leaf of pattern tree is also the root of some min cost matching pattern

- ▶ Leads to a recursive algorithm

- ▶ ( A dynamic programming algorithm, if you know that terminology...)

- **▼** Pick an illustrative example to see how this works

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 29

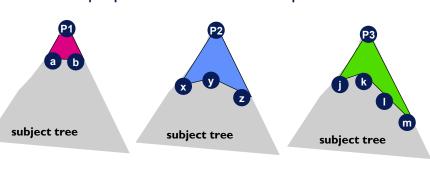

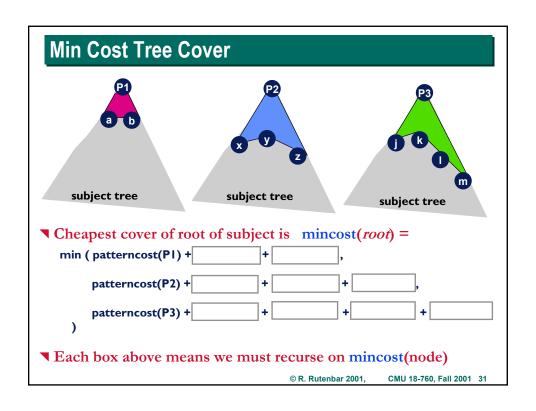

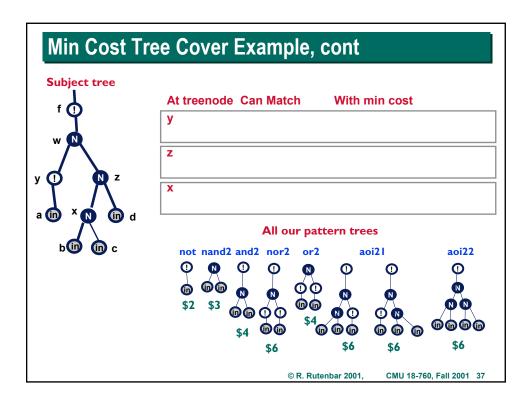

# **Min Cost Tree Covering**

- Assume 3 different patterns match at *root* of subject

- ▶ Pattern PI has 2 leaf nodes: a b

- ▶ Pattern P2 has 3 leaf nodes: x y z

- ▶ Pattern P3 has 4 leaf nodes: j k l m

- ▶ Which is cheapest pattern if we know cost of each pattern?

© R. Rutenbar 2001,

# **Min Cost Tree Cover**

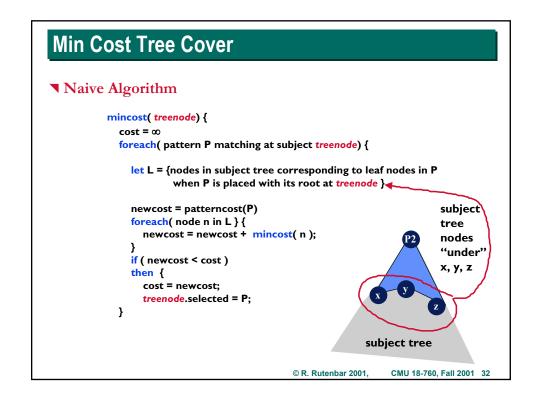

### **■** What's wrong with this?

- ▶ Will revisit same treenode many times during recursions...

- ▶ ...and it will recompute the min cost cover for that node each time.

#### **▼** Can we do *better...*?

- ▶ Sure, just keep a table with min cost for each node

- ► Starts with value ∞ and then when the node's cost get computed, this value gets updated

- ► Check first to see if the node has already been visited before computing it--saves computing it multiple times.

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 33

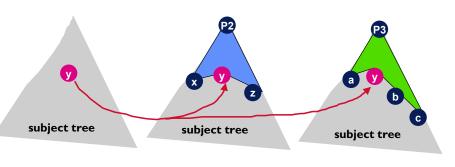

# Illustration

### Node "y" in this subject tree

- ▶ Will get its mincost cover computed (mincost(y)) when we put P2 at the root of the subject tree...

- ▶ ...and again when we put P3 at the root

- ▶ Why not just compute it once, first time, save it, and look it up later?

© R. Rutenbar 2001,

# Min Cost Tree Cover

### **▼** Improved

▶ Assume table[] gets set up so table[node] = ∞ for all nodes at start

```

mincost( treenode) {

if (table[treenode]) < \infty

then return( table[treenode]);

cost = \infty

foreach( pattern P matching at subject treenode) {

let L = {nodes in subject tree corresponding to leaf nodes in P

when P is placed with its root at treenode }

newcost = patterncost(P)

foreach( node n in L ) {

newcost = newcost + mincost( n );

if ( newcost < cost )</pre>

then {

cost = newcost; table[treenode] = newcost

treenode.selected = P;

}

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 35

```

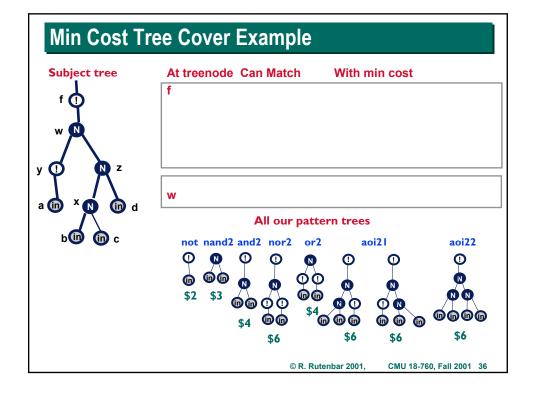

# **Min Cost Tree Cover**

### ▼ Example

- ▶ If costs for NOT, NAND2, AND2, AOI21 are as shown...

- ▶ Best cover is to use one AOI21 and one NAND2

### **▼** Turns out to be several nice extensions possible

- ▶ Can tweak algorithm a little to minimize delay instead of cost

- ▶ Need to deal with some messy issues associated with capacitive loads for driven gates, but some simple discrete loads can be modeled and handled.

© R. Rutenbar 2001,

### **Issues**

#### **▼** Pro

- ► Easy, simple algorithm

- ▶ Works great for trees

#### **▼** Con

- ▶ Not everything is a tree

- ▶ Most subject netlists are NOT trees, need to chop up into trees

- ▶ Some patterns cannot be trees (EXOR, MUX)

#### **▼** Comments

- ▶ Heuristic tricks for dealing with most of these

- ▶ Also, other tech mapping approaches

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 39

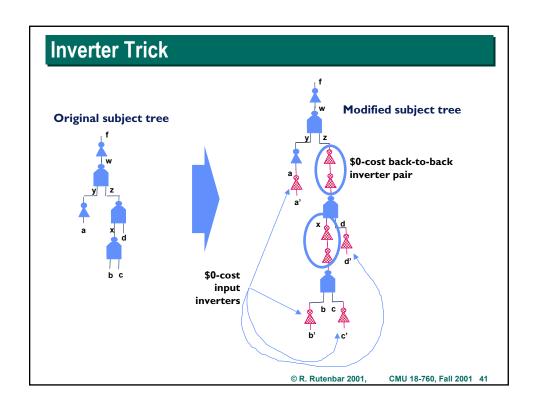

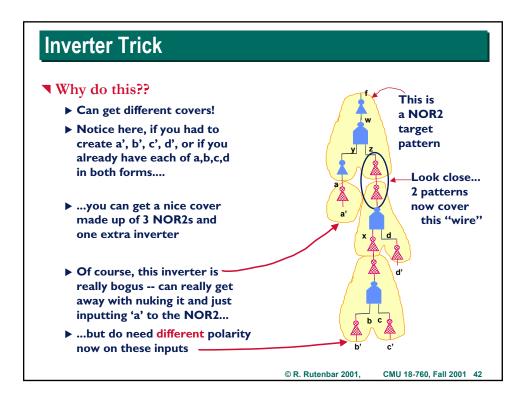

## **Polarity Assignment**

### **▼** One cool trick worth mentioning

- ▶ What if you can't match a pattern just because you don't have the right polarities (true / complemented form) on internal nodes of subject tree?

- ▶ Just don't use that good pattern? No -- fix the polarity

#### **■** Do this to netlist

- ▶ At every internal wire in netlist (from a gate output to a gate input) where there is no inverter, replace with back-to-back inverters

- ▶ At every input, add one more zero-cost-inverter

### **■** Do this to pattern library

- ► Add back-to-back inverter pattern with cost = 0, on every internal wire (from a gate output to a gate input) in your pattern trees

- ▶ Add zero-cost-inverter pattern, only matches at inputs, cost=0

© R. Rutenbar 2001, CMU 18-760, Fall 2001 40

# **Summary**

### **▼** Technology mapping ...

- ► Synthesis gives you "uncommitted" or "technology independent" design, eg, NAND2 and NOT

- ▶ Mapping turns this into real gates in your own library

- ▶ Can determine difference between good implementation and a bad one

- ▶ Still a very hot problem

### **▼**Tree covering

- ▶ One nice, simple, elegant approach to the problem

- ▶ 3 parts: tree-ify input, match all lib patterns, find min cost cover

#### **▼**Tricks

▶ Adding extra inverters (with cost) can get you out of nasty problems where a nice pattern does't match because of wrong polarity at inputs

© R. Rutenbar 2001, CMU 18-760, Fall 2001 43